TS-7250-V3 DIO Header: Difference between revisions

From embeddedTS Manuals

No edit summary |

No edit summary |

||

| Line 27: | Line 27: | ||

|- | |- | ||

| 6 | | 6 | ||

| [[#SPI|spidev 4.0 Chip Select]] | | [[#SPI|spidev 4.0 Chip Select]] / [[#GPIO|GPIO Bank 5 IO 11]] | ||

|- | |- | ||

| 7 | | 7 | ||

| Line 39: | Line 39: | ||

|- | |- | ||

| 10 | | 10 | ||

| [[#SPI|spidev 4.0 MISO]] | | [[#SPI|spidev 4.0 MISO]] / [[#GPIO|GPIO Bank 5 IO 10]] <ref>This pin is input only even when in the GPIO mode</ref> | ||

|- | |- | ||

| 11 | | 11 | ||

| Line 45: | Line 45: | ||

|- | |- | ||

| 12 | | 12 | ||

| [[#SPI|spidev 4.0 MOSI]] | | [[#SPI|spidev 4.0 MOSI]] / [[#GPIO|GPIO Bank 5 IO 15]] | ||

|- | |- | ||

| 13 | | 13 | ||

| Line 51: | Line 51: | ||

|- | |- | ||

| 14 | | 14 | ||

| [[#SPI|spidev 4.0 CLK]] | | [[#SPI|spidev 4.0 CLK]] / [[#GPIO|GPIO Bank 5 IO 14]] | ||

|- | |- | ||

| 15 | | 15 | ||

Revision as of 10:31, 21 July 2022

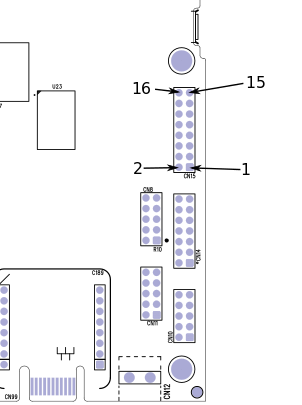

The DIO header is a 0.1" pitch 2x8 header including SPI and GPIO. All pins on this header are 5V tolerant except SPI output pins. All of these DIO includes pullups.

| Signals | Pin Layout | ||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

The DIO header is designed to provide compatibility with the KPAD accessory. This is a 4x4 numerical keypad. This is supported in userspace with the keypad.c source code, or the "keypad" utility which is included in the shiping image.

This debounces presses to 50ms, and does not repeat when numbers are held. This will output a string containing the key that is pressed. Eg:

root@tsimx6:~# keypad 1 UP DOWN 2ND ENTER