TS-7250-V3 LCD Header: Difference between revisions

From embeddedTS Manuals

m (Links auto-updated for 2022 re-branding ( https://github.com/embeddedarm/ts7100-utils/blob/master/src/lcdmesg.c → https://github.com/embeddedTS/ts7100-utils/blob/master/src/lcdmesg.c https://www.embeddedarm.com/parts/LCD-LED → https://www.embeddedTS.com/parts/LCD-LED)) |

No edit summary |

||

| Line 30: | Line 30: | ||

|- | |- | ||

! Pin | ! Pin | ||

! IO Type | |||

! Signal | ! Signal | ||

|- | |- | ||

| 1 | | 1 | ||

| | |||

| [[#Board Rails|5V]] | | [[#Board Rails|5V]] | ||

|- | |- | ||

| 2 | | 2 | ||

| | |||

| GND | | GND | ||

|- | |- | ||

| 3 | | 3 | ||

| [[#IO specifications|CPU 3.3V]] | |||

| LCD_RS [[#GPIO|GPIO Bank 2 IO 21]] | | LCD_RS [[#GPIO|GPIO Bank 2 IO 21]] | ||

|- | |- | ||

| 4 | | 4 | ||

| [[#IO specifications|CPU 3.3V]] | |||

| LCD_BIAS <ref>PWM duty cycle controlled by [[#FPGA Syscon|FPGA Syscon reg 0x1c]]. This may need to be tuned depending on the environment or altitude where the display is used.</ref> | | LCD_BIAS <ref>PWM duty cycle controlled by [[#FPGA Syscon|FPGA Syscon reg 0x1c]]. This may need to be tuned depending on the environment or altitude where the display is used.</ref> | ||

|- | |- | ||

| 5 | | 5 | ||

| [[#IO specifications|CPU 3.3V]] | |||

| LCD_EN [[#GPIO|GPIO Bank 5 IO 20]] | | LCD_EN [[#GPIO|GPIO Bank 5 IO 20]] | ||

|- | |- | ||

| 6 | | 6 | ||

| [[#IO specifications|CPU 3.3V]] | |||

| LCD_WR [[#GPIO|GPIO Bank 5 IO 19]] | | LCD_WR [[#GPIO|GPIO Bank 5 IO 19]] | ||

|- | |- | ||

| 7 | | 7 | ||

| [[#IO specifications|CPU 3.3V+QS3861]] | |||

| LCD D1 [[#GPIO|GPIO Bank 2 IO 9]] | | LCD D1 [[#GPIO|GPIO Bank 2 IO 9]] | ||

|- | |- | ||

| 8 | | 8 | ||

| [[#IO specifications|CPU 3.3V+QS3861]] | |||

| LCD D0 [[#GPIO|GPIO Bank 5 IO 10]] | | LCD D0 [[#GPIO|GPIO Bank 5 IO 10]] | ||

|- | |- | ||

| 9 | | 9 | ||

| [[#IO specifications|CPU 3.3V+QS3861]] | |||

| LCD D3 [[#GPIO|GPIO Bank 5 IO 11]] | | LCD D3 [[#GPIO|GPIO Bank 5 IO 11]] | ||

|- | |- | ||

| 10 | | 10 | ||

| [[#IO specifications|CPU 3.3V+QS3861]] | |||

| LCD D2 [[#GPIO|GPIO Bank 5 IO 12]] | | LCD D2 [[#GPIO|GPIO Bank 5 IO 12]] | ||

|- | |- | ||

| 11 | | 11 | ||

| [[#IO specifications|CPU 3.3V+QS3861]] | |||

| LCD D5 [[#GPIO|GPIO Bank 5 IO 15]] | | LCD D5 [[#GPIO|GPIO Bank 5 IO 15]] | ||

|- | |- | ||

| 12 | | 12 | ||

| [[#IO specifications|CPU 3.3V+QS3861]] | |||

| LCD D4 [[#GPIO|GPIO Bank 5 IO 16]] | | LCD D4 [[#GPIO|GPIO Bank 5 IO 16]] | ||

|- | |- | ||

| 13 | | 13 | ||

| [[#IO specifications|CPU 3.3V+QS3861]] | |||

| LCD_D7 [[#GPIO|GPIO Bank 5 IO 17]] | | LCD_D7 [[#GPIO|GPIO Bank 5 IO 17]] | ||

|- | |- | ||

| 14 | | 14 | ||

| [[#IO specifications|CPU 3.3V+QS3861]] | |||

| LCD_D6 [[#GPIO|GPIO Bank 5 IO 18]] | | LCD_D6 [[#GPIO|GPIO Bank 5 IO 18]] | ||

|} | |} | ||

Revision as of 16:02, 22 September 2023

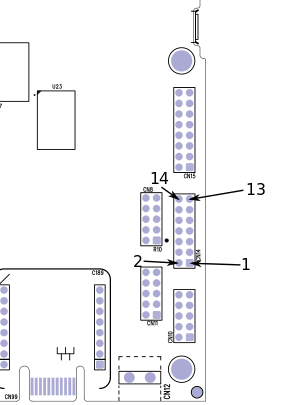

The LCD header is a 0.1" pitch 2x7 header including GPIO. This is designed around compatibility with the HD44780 LCD controller which includes our LCD-LED. The LCD Data pins (7-14) are 5V tolerant. These will output up to 3.3V, and the remaining control IO and PWM are 3.3V tolerant. The TS-7250-V3 Debian images include a command lcdmesg. This can be used to write to our LCD-LED display.

For example, this would write to the display:

lcdmesg "line 1" "line 2"

# Messages can also be piped to lcdmesg:

echo -e "line 1\nline 2\n" | lcdmesg

For example, running:

lcdmesg Technologic Systems

will display:

Pin 4, the LCD_BIAS pin, is used to set the contrast on the LCD.

tshwctl --address 0x1c --poke16 0x0 # Writes minimum

tshwctl --address 0x1c --poke16 0xf # Writes maximum

| Signals | Pin Layout | |||||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

- ↑ PWM duty cycle controlled by FPGA Syscon reg 0x1c. This may need to be tuned depending on the environment or altitude where the display is used.