TS-7250-V3 ADC Header: Difference between revisions

From embeddedTS Manuals

No edit summary |

No edit summary |

||

| (2 intermediate revisions by the same user not shown) | |||

| Line 1: | Line 1: | ||

The ADC header supports 5 channels of 0-30VDC ADC. Of these 5, 3 channels support sampling 0-20mA current loops. These channels are sampled from | The ADC header supports 5 channels of 0-30VDC ADC. Of these 5, 3 channels support sampling 0-20mA current loops. These channels are sampled from: | ||

<source lang=bash> | |||

iio_attr -c 2198000.adc voltage0 | |||

iio_attr -c 2198000.adc voltage1 | |||

iio_attr -c 2198000.adc voltage5 | |||

iio_attr -c 2198000.adc voltage8 | |||

iio_attr -c 2198000.adc voltage9 | |||

</source> | |||

See the [[#ADC|ADC section]] for more details on sampling these pins. | |||

{| | {| | ||

| Line 13: | Line 21: | ||

|- | |- | ||

| 1 | | 1 | ||

| | | 2198000.adc/voltage0 | ||

|- | |- | ||

| 2 | | 2 | ||

| Line 19: | Line 27: | ||

|- | |- | ||

| 3 | | 3 | ||

| | | 2198000.adc/voltage1 | ||

|- | |- | ||

| 4 | | 4 | ||

| Line 25: | Line 33: | ||

|- | |- | ||

| 5 | | 5 | ||

| | | 2198000.adc/voltage5 | ||

|- | |- | ||

| 6 | | 6 | ||

| Line 31: | Line 39: | ||

|- | |- | ||

| 7 | | 7 | ||

| | | 2198000.adc/voltage8 | ||

|- | |- | ||

| 8 | | 8 | ||

| Line 37: | Line 45: | ||

|- | |- | ||

| 9 | | 9 | ||

| | | 2198000.adc/voltage9 [[#TS-7250-V3 Supervisory Low Power Mode|WAKE_UP#]] | ||

|- | |- | ||

| 10 | | 10 | ||

Latest revision as of 15:09, 6 April 2023

The ADC header supports 5 channels of 0-30VDC ADC. Of these 5, 3 channels support sampling 0-20mA current loops. These channels are sampled from:

iio_attr -c 2198000.adc voltage0

iio_attr -c 2198000.adc voltage1

iio_attr -c 2198000.adc voltage5

iio_attr -c 2198000.adc voltage8

iio_attr -c 2198000.adc voltage9

See the ADC section for more details on sampling these pins.

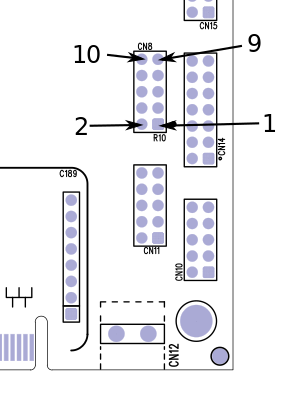

| Signals | Pin Layout | ||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|