TS-7250-V3 MikroBus Header: Difference between revisions

From embeddedTS Manuals

No edit summary |

No edit summary |

||

| Line 1: | Line 1: | ||

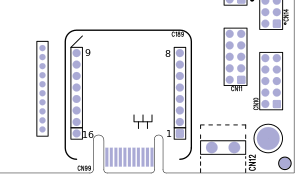

The Mikrobus header is a 0.1" pitch 2x8 header which supports [https://www.mikroe.com/click the Mikroe Click board ecosystem]. This header features 3.3V, 5V, SPI, GPIO, ADC, PWM, a UART, and PWM. All IO are 3.3V tolerant. | The Mikrobus header is a 0.1" pitch 2x8 header which supports [https://www.mikroe.com/click the Mikroe Click board ecosystem]. This header features 3.3V, 5V, SPI, GPIO, ADC, PWM, a UART, and PWM. All IO are 3.3V tolerant. | ||

By default all of these headers default to their non-gpio functions. These can be changed in the [[#FPGA Syscon|FPGA syscon register 0x08]]. For example: | |||

<source lang=bash> | |||

# Make all mikrobus header pins GPIO: | |||

peekpoke 32 0x50004008 0xF0 | |||

# Set only SPI to GPIO: | |||

peekpoke 32 0x50004008 0x10 | |||

</source> | |||

{| | {| | ||

| Line 12: | Line 21: | ||

|- | |- | ||

| 1 | | 1 | ||

| | | [[#FPGA_ADC]] | ||

|- | |- | ||

| 2 | | 2 | ||

| Line 18: | Line 27: | ||

|- | |- | ||

| 3 | | 3 | ||

| [[#FPGA_SPI|spidev 5.0 CS#]] | | [[#FPGA_SPI|spidev 5.0 CS#]] / [[#GPIO|GPIO Bank 7 IO 5]] | ||

|- | |- | ||

| 4 | | 4 | ||

| [[#FPGA_SPI|spidev 5.0 CLK]] | | [[#FPGA_SPI|spidev 5.0 CLK]] / [[#GPIO|GPIO Bank 7 IO 6]] | ||

|- | |- | ||

| 5 | | 5 | ||

| [[#FPGA_SPI|spidev 5.0 MISO]] | | [[#FPGA_SPI|spidev 5.0 MISO]] / [[#GPIO|GPIO Bank 7 IO 7]] | ||

|- | |- | ||

| 6 | | 6 | ||

| [[#FPGA_SPI|spidev 5.0 MOSI]] | | [[#FPGA_SPI|spidev 5.0 MOSI]] / [[#GPIO|GPIO Bank 7 IO 8]] | ||

|- | |- | ||

| 7 | | 7 | ||

| Line 42: | Line 51: | ||

|- | |- | ||

| 11 | | 11 | ||

| [[#I2C|/dev/i2c-2 DAT]] | | [[#I2C|/dev/i2c-2 DAT]] / [[#GPIO|GPIO Bank 7 IO 11]] | ||

|- | |- | ||

| 12 | | 12 | ||

| [[#I2C|/dev/i2c-2 CLK]] | | [[#I2C|/dev/i2c-2 CLK]] / [[#GPIO|GPIO Bank 7 IO 12]] | ||

|- | |- | ||

| 13 | | 13 | ||

| [[#UARTs|ttymxc6 TXD]] | | [[#UARTs|ttymxc6 TXD]] / [[#GPIO|GPIO Bank 7 IO 9]] | ||

|- | |- | ||

| 14 | | 14 | ||

| [[#UARTs|ttymxc6 RXD]] | | [[#UARTs|ttymxc6 RXD]] / [[#GPIO|GPIO Bank 7 IO 10]] | ||

|- | |- | ||

| 15 | | 15 | ||

| | | [[#FPGA IRQs|FPGA IRQ 18]] / [[#GPIO|GPIO Bank 7 IO 2]] | ||

|- | |- | ||

| 16 | | 16 | ||

| MIKRO_PWM | | [[#FPGA PWM|MIKRO_PWM]] / [[#GPIO|GPIO Bank 7 IO 4]] | ||

|} | |} | ||

| | | | ||

Revision as of 09:28, 6 October 2021

The Mikrobus header is a 0.1" pitch 2x8 header which supports the Mikroe Click board ecosystem. This header features 3.3V, 5V, SPI, GPIO, ADC, PWM, a UART, and PWM. All IO are 3.3V tolerant.

By default all of these headers default to their non-gpio functions. These can be changed in the FPGA syscon register 0x08. For example:

# Make all mikrobus header pins GPIO:

peekpoke 32 0x50004008 0xF0

# Set only SPI to GPIO:

peekpoke 32 0x50004008 0x10

| Signals | Pin Layout | ||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|