TS-7250-V3 PC104 Bus Timing: Difference between revisions

From embeddedTS Manuals

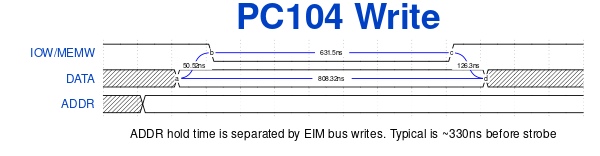

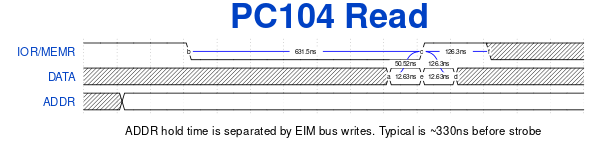

(Created page with "The TS-7250-V3 PC104 cycles are approximately 1us per access, on either 8 or 16-bit. The timing is not user configurable, but is known to work with most typical ISA compatibl...") |

No edit summary |

||

| Line 4: | Line 4: | ||

| [[File:TS-7250-V3 PC104 Write Strobe.svg|600px]] | | [[File:TS-7250-V3 PC104 Write Strobe.svg|600px]] | ||

|- | |- | ||

| [[File:TS-7250-V3 PC104 | | [[File:TS-7250-V3 PC104 Read Strobe.svg|600px]] | ||

|} | |} | ||