TS-7250-V3 PC104 Bus Timing: Difference between revisions

From embeddedTS Manuals

No edit summary |

No edit summary |

||

| Line 2: | Line 2: | ||

{| | {| | ||

<!-- | |||

{ | |||

head: { text: | |||

['tspan', | |||

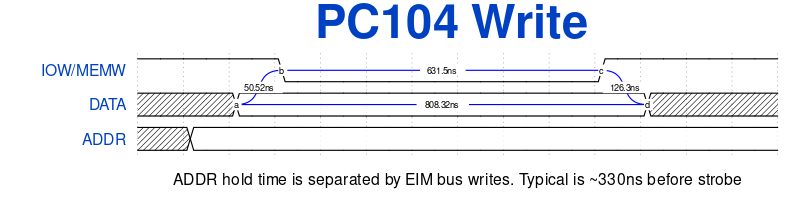

['tspan', {class:'info h1'}, 'PC104 Write '], | |||

] | |||

}, | |||

signal: [ | |||

{ name: "IOW/MEMW", wave: "1..0......1...", node: "...b......c..." }, | |||

{ name: "DATA", wave: "x.2........x..", node: "..a........d.."}, | |||

{ name: "ADDR", wave: "x2............" } | |||

], | |||

edge: [ | |||

'a~b 40.4ns', | |||

'b~c 505ns', | |||

'c~d 101ns' | |||

], | |||

foot: { text: | |||

['tspan', 'ADDR hold time is separated by EIM bus writes. Typical is ~330ns before strobe'], | |||

} | |||

} | |||

--> | |||

| [[File:TS-7250-V3 PC104 Write Strobe.svg|800px]] | | [[File:TS-7250-V3 PC104 Write Strobe.svg|800px]] | ||

|- | |- | ||

<!-- | |||

{ | |||

head: { text: | |||

['tspan', | |||

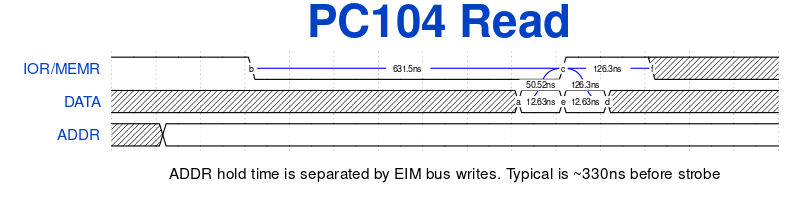

['tspan', {class:'info h1'}, 'PC104 Read '], | |||

] | |||

}, | |||

signal: [ | |||

{ name: "IOR/MEMR", wave: "1..0......1....", node: "...b......c.f." }, | |||

{ name: "DATA", wave: "x........==x...", node: ".........aed.."}, | |||

{ name: "ADDR", wave: "x2............." } | |||

], | |||

edge: [ | |||

'b-c 505ns', | |||

'c~d 101ns', | |||

'c~a 40.4ns', | |||

'a~e 10.1ns', | |||

'e~d 10.1ns', | |||

'c~f 101ns', | |||

], | |||

foot: { text: | |||

['tspan', 'ADDR hold time is separated by EIM bus writes. Typical is ~330ns before strobe'], | |||

} | |||

} | |||

--> | |||

| [[File:TS-7250-V3 PC104 Read Strobe.svg|800px]] | | [[File:TS-7250-V3 PC104 Read Strobe.svg|800px]] | ||

|} | |} | ||