TS-7250-V3 PC104 Header: Difference between revisions

From embeddedTS Manuals

No edit summary |

No edit summary |

||

| Line 35: | Line 35: | ||

| A31 | | A31 | ||

| ISA_ADD_00 | | ISA_ADD_00 | ||

| | | [[#GPIO|Bank 9 IO 0]] | ||

|- | |- | ||

| B30 | | B30 | ||

| Line 43: | Line 43: | ||

| A30 | | A30 | ||

| ISA_ADD_01 | | ISA_ADD_01 | ||

| | | [[#GPIO|Bank 9 IO 1]] | ||

|- | |- | ||

| B29 | | B29 | ||

| Line 51: | Line 51: | ||

| A29 | | A29 | ||

| ISA_ADD_02 | | ISA_ADD_02 | ||

| | | [[#GPIO|Bank 9 IO 2]] | ||

|- | |- | ||

| B28 | | B28 | ||

| Line 59: | Line 59: | ||

| A28 | | A28 | ||

| ISA_ADD_03 | | ISA_ADD_03 | ||

| | | [[#GPIO|Bank 9 IO 3]] | ||

| | | | ||

| C19 | | C19 | ||

| Line 75: | Line 75: | ||

| A27 | | A27 | ||

| ISA_ADD_04 | | ISA_ADD_04 | ||

| | | [[#GPIO|Bank 9 IO 4]] | ||

| | | | ||

| C18 | | C18 | ||

| ISA_DAT_15 | | ISA_DAT_15 | ||

| | | [[#GPIO|Bank 8 IO 15]] | ||

| | | | ||

| D18 | | D18 | ||

| Line 91: | Line 91: | ||

| A26 | | A26 | ||

| ISA_ADD_05 | | ISA_ADD_05 | ||

| | | [[#GPIO|Bank 9 IO 5]] | ||

| | | | ||

| C17 | | C17 | ||

| ISA_DAT_14 | | ISA_DAT_14 | ||

| | | [[#GPIO|Bank 8 IO 14]] | ||

| | | | ||

| D17 | | D17 | ||

| Line 107: | Line 107: | ||

| A25 | | A25 | ||

| ISA_ADD_06 | | ISA_ADD_06 | ||

| | | [[#GPIO|Bank 9 IO 6]] | ||

| | | | ||

| C16 | | C16 | ||

| ISA_DAT_13 | | ISA_DAT_13 | ||

| | | [[#GPIO|Bank 8 IO 13]] | ||

| | | | ||

| D16 | | D16 | ||

| Line 123: | Line 123: | ||

| A24 | | A24 | ||

| ISA_ADD_07 | | ISA_ADD_07 | ||

| | | [[#GPIO|Bank 9 IO 7]] | ||

| | | | ||

| C15 | | C15 | ||

| ISA_DAT_12 | | ISA_DAT_12 | ||

| | | [[#GPIO|Bank 8 IO 12]] | ||

| | | | ||

| D15 | | D15 | ||

| Line 139: | Line 139: | ||

| A23 | | A23 | ||

| ISA_ADD_08 | | ISA_ADD_08 | ||

| | | [[#GPIO|Bank 9 IO 8]] | ||

| | | | ||

| C14 | | C14 | ||

| ISA_DAT_11 | | ISA_DAT_11 | ||

| | | [[#GPIO|Bank 8 IO 11]] | ||

| | | | ||

| D14 | | D14 | ||

| Line 155: | Line 155: | ||

| A22 | | A22 | ||

| ISA_ADD_09 | | ISA_ADD_09 | ||

| | | [[#GPIO|Bank 9 IO 9]] | ||

| | | | ||

| C13 | | C13 | ||

| ISA_DAT_10 | | ISA_DAT_10 | ||

| | | [[#GPIO|Bank 8 IO 10]] | ||

| | | | ||

| D13 | | D13 | ||

| Line 171: | Line 171: | ||

| A21 | | A21 | ||

| ISA_ADD_10 | | ISA_ADD_10 | ||

| | | [[#GPIO|Bank 9 IO 10]] | ||

| | | | ||

| C12 | | C12 | ||

| ISA_DAT_09 | | ISA_DAT_09 | ||

| | | [[#GPIO|Bank 8 IO 9]] | ||

| | | | ||

| D12 | | D12 | ||

| Line 187: | Line 187: | ||

| A20 | | A20 | ||

| ISA_ADD_11 | | ISA_ADD_11 | ||

| | | [[#GPIO|Bank 9 IO 11]] | ||

| | | | ||

| C11 | | C11 | ||

| ISA_DAT_08 | | ISA_DAT_08 | ||

| | | [[#GPIO|Bank 8 IO 8]] | ||

| | | | ||

| D11 | | D11 | ||

| Line 203: | Line 203: | ||

| A19 | | A19 | ||

| ISA_ADD_12 | | ISA_ADD_12 | ||

| | | [[#GPIO|Bank 9 IO 12]] | ||

| | | | ||

| C10 | | C10 | ||

| Line 219: | Line 219: | ||

| A18 | | A18 | ||

| ISA_ADD_13 | | ISA_ADD_13 | ||

| | | [[#GPIO|Bank 9 IO 13]] | ||

| | | | ||

| C09 | | C09 | ||

| Line 231: | Line 231: | ||

| B17 | | B17 | ||

| ISA_DACK1 | | ISA_DACK1 | ||

| | | [[#GPIO|Bank 6 IO 8]] | ||

| | | | ||

| A17 | | A17 | ||

| ISA_ADD_14 | | ISA_ADD_14 | ||

| | | [[#GPIO|Bank 9 IO 14]] | ||

| | | | ||

| C08 | | C08 | ||

| Line 251: | Line 251: | ||

| A16 | | A16 | ||

| ISA_ADD_15 | | ISA_ADD_15 | ||

| | | [[#GPIO|Bank 9 IO 15]] | ||

| | | | ||

| C07 | | C07 | ||

| Line 267: | Line 267: | ||

| A15 | | A15 | ||

| ISA_ADD_16 | | ISA_ADD_16 | ||

| | | [[#GPIO|Bank 10 IO 0]] | ||

| | | | ||

| C06 | | C06 | ||

| Line 279: | Line 279: | ||

| B14 | | B14 | ||

| ISA_IOR | | ISA_IOR | ||

| | | [[#GPIO|Bank 10 IO 4]] | ||

| | | | ||

| A14 | | A14 | ||

| ISA_ADD_17 | | ISA_ADD_17 | ||

| | | [[#GPIO|Bank 10 IO 1]] | ||

| | | | ||

| C05 | | C05 | ||

| Line 295: | Line 295: | ||

| B13 | | B13 | ||

| ISA_IOW | | ISA_IOW | ||

| | | [[#GPIO|Bank 10 IO 5]] | ||

| | | | ||

| A13 | | A13 | ||

| ISA_ADD_18 | | ISA_ADD_18 | ||

| | | [[#GPIO|Bank 10 IO 2]] | ||

| | | | ||

| C04 | | C04 | ||

| Line 311: | Line 311: | ||

| B12 | | B12 | ||

| ISA_MEMR | | ISA_MEMR | ||

| | | [[#GPIO|Bank 10 IO 6]] | ||

| | | | ||

| A12 | | A12 | ||

| ISA_ADD_19 | | ISA_ADD_19 | ||

| | | [[#GPIO|Bank 10 IO 3]] | ||

| | | | ||

| C03 | | C03 | ||

| Line 327: | Line 327: | ||

| B11 | | B11 | ||

| ISA_MEMW | | ISA_MEMW | ||

| | | [[#GPIO|Bank 10 IO 7]] | ||

| | | | ||

| A11 | | A11 | ||

| ISA_AEN | | ISA_AEN | ||

| | | [[#GPIO|Bank 6 IO 0]] | ||

| | | | ||

| C02 | | C02 | ||

| Line 339: | Line 339: | ||

| D02 | | D02 | ||

| ISA_IO16 | | ISA_IO16 | ||

| | | [[#GPIO|Bank 10 IO 9]] | ||

|- | |- | ||

| B10 | | B10 | ||

| Line 355: | Line 355: | ||

| D01 | | D01 | ||

| ISA_MEM16 | | ISA_MEM16 | ||

| | | [[#GPIO|Bank 10 IO 8]] | ||

|- | |- | ||

| B09 | | B09 | ||

| Line 363: | Line 363: | ||

| A09 | | A09 | ||

| ISA_DAT_00 | | ISA_DAT_00 | ||

| | | [[#GPIO|Bank 8 IO 0]] | ||

| | | | ||

| C00 | | C00 | ||

| Line 379: | Line 379: | ||

| A08 | | A08 | ||

| ISA_DAT_01 | | ISA_DAT_01 | ||

| | | [[#GPIO|Bank 8 IO 1]] | ||

| rowspan=8 colspan=8 | | | rowspan=8 colspan=8 | | ||

|- | |- | ||

| Line 388: | Line 388: | ||

| A07 | | A07 | ||

| ISA_DAT_03 | | ISA_DAT_03 | ||

| | | [[#GPIO|Bank 8 IO 3]] | ||

|- | |- | ||

| B06 | | B06 | ||

| Line 396: | Line 396: | ||

| A06 | | A06 | ||

| ISA_DAT_04 | | ISA_DAT_04 | ||

| | | [[#GPIO|Bank 8 IO 4]] | ||

|- | |- | ||

| B05 | | B05 | ||

| Line 404: | Line 404: | ||

| A05 | | A05 | ||

| ISA_DAT_05 | | ISA_DAT_05 | ||

| | | [[#GPIO|Bank 8 IO 5]] | ||

|- | |- | ||

| B04 | | B04 | ||

| Line 412: | Line 412: | ||

| A04 | | A04 | ||

| ISA_DAT_02 | | ISA_DAT_02 | ||

| | | [[#GPIO|Bank 8 IO 2]] | ||

|- | |- | ||

| B03 | | B03 | ||

| Line 420: | Line 420: | ||

| A03 | | A03 | ||

| ISA_DAT_06 | | ISA_DAT_06 | ||

| | | [[#GPIO|Bank 8 IO 6]] | ||

|- | |- | ||

| B02 | | B02 | ||

| Line 428: | Line 428: | ||

| A02 | | A02 | ||

| ISA_DAT_07 | | ISA_DAT_07 | ||

| | | [[#GPIO|Bank 8 IO 7]] | ||

|- | |- | ||

| B01 | | B01 | ||

Revision as of 10:24, 16 December 2021

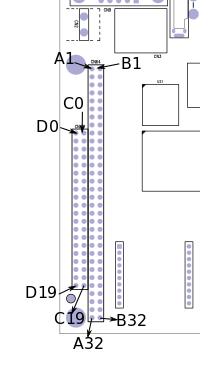

The PC104 connector consists of four rows of pins labelled A-D. The PC104 standard implements an ISA bus over these headers, but we also include the ability for almost all of the pins to be used as DIO.

| Pin | Name | GPIO | Pin | Name | GPIO | Pin | Name | GPIO | Pin | Name | GPIO | |||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| B32 | GND | N/A | A32 | GND | N/A | |||||||||

| B31 | GND | N/A | A31 | ISA_ADD_00 | Bank 9 IO 0 | |||||||||

| B30 | ISA_14_3_MHZ | N/A | A30 | ISA_ADD_01 | Bank 9 IO 1 | |||||||||

| B29 | 5V | N/A | A29 | ISA_ADD_02 | Bank 9 IO 2 | |||||||||

| B28 | ISA_BALE | Bank 6 IO 1 | A28 | ISA_ADD_03 | Bank 9 IO 3 | C19 | GND | N/A | D19 | GND | N/A | |||

| B27 | ISA_TC | Bank 6 IO 2 | A27 | ISA_ADD_04 | Bank 9 IO 4 | C18 | ISA_DAT_15 | Bank 8 IO 15 | D18 | GND | N/A | |||

| B26 | ISA_DACK2 | Bank 6 IO 10 | A26 | ISA_ADD_05 | Bank 9 IO 5 | C17 | ISA_DAT_14 | Bank 8 IO 14 | D17 | Unused | N/A | |||

| B25 | ISA_IRQ3 | N/A | A25 | ISA_ADD_06 | Bank 9 IO 6 | C16 | ISA_DAT_13 | Bank 8 IO 13 | D16 | +5V | N/A | |||

| B24 | GND | N/A | A24 | ISA_ADD_07 | Bank 9 IO 7 | C15 | ISA_DAT_12 | Bank 8 IO 12 | D15 | ISA_DRQ7 | Bank 7 IO 12 | |||

| B23 | ISA_IRQ5 | N/A | A23 | ISA_ADD_08 | Bank 9 IO 8 | C14 | ISA_DAT_11 | Bank 8 IO 11 | D14 | ISA_DACK7 | Bank 7 IO 11 | |||

| B22 | ISA_IRQ6 | N/A | A22 | ISA_ADD_09 | Bank 9 IO 9 | C13 | ISA_DAT_10 | Bank 8 IO 10 | D13 | ISA_DRQ6 | Bank 7 IO 10 | |||

| B21 | ISA_IRQ7 | N/A | A21 | ISA_ADD_10 | Bank 9 IO 10 | C12 | ISA_DAT_09 | Bank 8 IO 9 | D12 | ISA_DACK6 | Bank 7 IO 9 | |||

| B20 | ISA_BCLK | N/A | A20 | ISA_ADD_11 | Bank 9 IO 11 | C11 | ISA_DAT_08 | Bank 8 IO 8 | D11 | ISA_DRQ5 | Bank 7 IO 8 | |||

| B19 | ISA_REFRESH | Bank 6 IO 6 | A19 | ISA_ADD_12 | Bank 9 IO 12 | C10 | Unused | N/A | D10 | ISA_DACK5 | Bank 7 IO 7 | |||

| B18 | ISA_DRQ1 | Bank 6 IO 7 | A18 | ISA_ADD_13 | Bank 9 IO 13 | C09 | Unused | N/A | D09 | ISA_DRQ0 | Bank 7 IO 6 | |||

| B17 | ISA_DACK1 | Bank 6 IO 8 | A17 | ISA_ADD_14 | Bank 9 IO 14 | C08 | Unused | N/A | D08 | ISA_DACK0 | Bank 7 IO 5 | |||

| B16 | ISA_DRQ3 | Bank 6 IO 12 | A16 | ISA_ADD_15 | Bank 9 IO 15 | C07 | Unused | N/A | D07 | ISA_IRQ14 | Bank 7 IO 4 | |||

| B15 | ISA_DACK3 | Bank 6 IO 13 | A15 | ISA_ADD_16 | Bank 10 IO 0 | C06 | Unused | N/A | D06 | ISA_IRQ15 | Bank 7 IO 3 | |||

| B14 | ISA_IOR | Bank 10 IO 4 | A14 | ISA_ADD_17 | Bank 10 IO 1 | C05 | N/A | Unused | D05 | ISA_IRQ12 | Bank 7 IO 2 | |||

| B13 | ISA_IOW | Bank 10 IO 5 | A13 | ISA_ADD_18 | Bank 10 IO 2 | C04 | Unused | N/A | D04 | ISA_IRQ11 | Bank 7 IO 1 | |||

| B12 | ISA_MEMR | Bank 10 IO 6 | A12 | ISA_ADD_19 | Bank 10 IO 3 | C03 | Unused | N/A | D03 | ISA_IRQ10 | Bank 7 IO 0 | |||

| B11 | ISA_MEMW | Bank 10 IO 7 | A11 | ISA_AEN | Bank 6 IO 0 | C02 | Unused | N/A | D02 | ISA_IO16 | Bank 10 IO 9 | |||

| B10 | GND | N/A | A10 | ISA_IORDY | Bank 6 IO 5 | C01 | Unused | N/A | D01 | ISA_MEM16 | Bank 10 IO 8 | |||

| B09 | Unused | N/A | A09 | ISA_DAT_00 | Bank 8 IO 0 | C00 | GND | N/A | D00 | GND | N/A | |||

| B08 | ISA_ENDX | Bank 6 IO 3 | A08 | ISA_DAT_01 | Bank 8 IO 1 | |||||||||

| B07 | Unused | N/A | A07 | ISA_DAT_03 | Bank 8 IO 3 | |||||||||

| B06 | ISA_DRQ2 | Bank 6 IO 9 | A06 | ISA_DAT_04 | Bank 8 IO 4 | |||||||||

| B05 | 3.3V [1] | N/A | A05 | ISA_DAT_05 | Bank 8 IO 5 | |||||||||

| B04 | ISA_IRQ9 | N/A | A04 | ISA_DAT_02 | Bank 8 IO 2 | |||||||||

| B03 | Unused | N/A | A03 | ISA_DAT_06 | Bank 8 IO 6 | |||||||||

| B02 | ISA_RESET | Bank 2 IO 7 [2] | A02 | ISA_DAT_07 | Bank 8 IO 7 | |||||||||

| B01 | GND | N/A | A01 | ISA_IOCHK | Bank 2 IO 8 | |||||||||