TS-7250-V3 PC104 Header: Difference between revisions

From embeddedTS Manuals

No edit summary |

No edit summary |

||

| Line 5: | Line 5: | ||

{| class=wikitable | {| class=wikitable | ||

! Pin | ! Pin | ||

! Description | ! Description | ||

| | | | ||

! Pin | ! Pin | ||

! Description | ! Description | ||

| | | | ||

! Pin | ! Pin | ||

! Description | ! Description | ||

| | | | ||

! Pin | ! Pin | ||

! Description | ! Description | ||

|- | |- | ||

| B32 | | B32 | ||

| GND | | GND | ||

| | | | ||

| A32 | | A32 | ||

| GND | | GND | ||

| rowspan=4 colspan=8 | | | rowspan=4 colspan=8 | | ||

|- | |- | ||

| B31 | | B31 | ||

| GND | | GND | ||

| | | | ||

| A31 | | A31 | ||

| ISA_ADD_00 | | [[#PC104_Bus|ISA_ADD_00]]/[[#GPIO|Bank 9 IO 0]] | ||

|- | |- | ||

| B30 | | B30 | ||

| ISA_14_3_MHZ <ref>Outputs a continuous 14.318180 MHz clock</ref> | | ISA_14_3_MHZ <ref>Outputs a continuous 14.318180 MHz clock</ref> | ||

| | | | ||

| A30 | | A30 | ||

| ISA_ADD_01 | | [[#PC104_Bus|ISA_ADD_01]]/[[#GPIO|Bank 9 IO 1]] | ||

|- | |- | ||

| B29 | | B29 | ||

| +5V <ref name=pc1045v>Powering the system from PC104 5V prevents the Board's low power sleep mode from functioning.</ref> | | +5V <ref name=pc1045v>Powering the system from PC104 5V prevents the Board's low power sleep mode from functioning.</ref> | ||

| | | | ||

| A29 | | A29 | ||

| ISA_ADD_02 | | [[#PC104_Bus|ISA_ADD_02]/[[#GPIO|Bank 9 IO 2]] | ||

|- | |- | ||

| B28 | | B28 | ||

| [[#GPIO|Bank 6 IO 1]] | | [[#GPIO|Bank 6 IO 1]] | ||

| | | | ||

| A28 | | A28 | ||

| ISA_ADD_03 | | [[#PC104_Bus|ISA_ADD_03]]/[[#GPIO|Bank 9 IO 3]] | ||

| | | | ||

| C19 | | C19 | ||

| GND | | GND | ||

| | | | ||

| D19 | | D19 | ||

| GND | | GND | ||

|- | |- | ||

| B27 | | B27 | ||

| [[#GPIO|Bank 6 IO 2]] | | [[#GPIO|Bank 6 IO 2]] | ||

| | | | ||

| A27 | | A27 | ||

| ISA_ADD_04 | | [[#PC104_Bus|ISA_ADD_04]]/[[#GPIO|Bank 9 IO 4]] | ||

| | | | ||

| C18 | | C18 | ||

| ISA_DAT_15 | | [[#PC104_Bus|ISA_DAT_15]]/[[#GPIO|Bank 8 IO 15]] | ||

| | | | ||

| D18 | | D18 | ||

| GND | | GND | ||

|- | |- | ||

| B26 | | B26 | ||

| [[#GPIO|Bank 6 IO 10]] | | [[#GPIO|Bank 6 IO 10]] | ||

| | | | ||

| A26 | | A26 | ||

| ISA_ADD_05 | | [[#PC104_Bus|ISA_ADD_05]]/[[#GPIO|Bank 9 IO 5]] | ||

| | | | ||

| C17 | | C17 | ||

| ISA_DAT_14 | | [[#PC104_Bus|ISA_DAT_14]]/[[#GPIO|Bank 8 IO 14]] | ||

| | | | ||

| D17 | | D17 | ||

| Unused | | Unused | ||

|- | |- | ||

| B25 | | B25 | ||

| [[#FPGA_IRQs|FPGA IRQ 13]] | | [[#FPGA_IRQs|FPGA IRQ 13]] | ||

| | | | ||

| A25 | | A25 | ||

| ISA_ADD_06 | | [[#PC104_Bus|ISA_ADD_06]]/[[#GPIO|Bank 9 IO 6]] | ||

| | | | ||

| C16 | | C16 | ||

| ISA_DAT_13 | | [[#PC104_Bus|ISA_DAT_13]]/[[#GPIO|Bank 8 IO 13]] | ||

| | | | ||

| D16 | | D16 | ||

| +5V <ref name=pc1045v /> | | +5V <ref name=pc1045v /> | ||

|- | |- | ||

| B24 | | B24 | ||

| GND | | GND | ||

| | | | ||

| A24 | | A24 | ||

| ISA_ADD_07 | | [[#PC104_Bus|ISA_ADD_07]]/[[#GPIO|Bank 9 IO 7]] | ||

| | | | ||

| C15 | | C15 | ||

| ISA_DAT_12 | | [[#PC104_Bus|ISA_DAT_12]]/[[#GPIO|Bank 8 IO 12]] | ||

| | | | ||

| D15 | | D15 | ||

| [[#GPIO|Bank 7 IO 12]] | | [[#GPIO|Bank 7 IO 12]] | ||

|- | |- | ||

| B23 | | B23 | ||

| [[#FPGA_IRQs|FPGA IRQ 14]] | | [[#FPGA_IRQs|FPGA IRQ 14]] | ||

| | | | ||

| A23 | | A23 | ||

| ISA_ADD_08 | | [[#PC104_Bus|ISA_ADD_08]]/[[#GPIO|Bank 9 IO 8]] | ||

| | | | ||

| C14 | | C14 | ||

| ISA_DAT_11 | | [[#PC104_Bus|ISA_DAT_11]]/[[#GPIO|Bank 8 IO 11]] | ||

| | | | ||

| D14 | | D14 | ||

| [[#GPIO|Bank 7 IO 11]] | | [[#GPIO|Bank 7 IO 11]] | ||

|- | |- | ||

| B22 | | B22 | ||

| [[#FPGA_IRQs|FPGA IRQ 15]] | | [[#FPGA_IRQs|FPGA IRQ 15]] | ||

| | | | ||

| A22 | | A22 | ||

| ISA_ADD_09 | | [[#PC104_Bus|ISA_ADD_09 | ||

| [[#GPIO|Bank 9 IO 9]] | | [[#GPIO|Bank 9 IO 9]] | ||

| | | | ||

| C13 | | C13 | ||

| ISA_DAT_10 | | [[#PC104_Bus|ISA_DAT_10]]/[[#GPIO|Bank 8 IO 10]] | ||

| | | | ||

| D13 | | D13 | ||

| [[#GPIO|Bank 7 IO 10]] | | [[#GPIO|Bank 7 IO 10]] | ||

|- | |- | ||

| B21 | | B21 | ||

| [[#FPGA_IRQs|FPGA IRQ 16]] | | [[#FPGA_IRQs|FPGA IRQ 16]] | ||

| | | | ||

| Line 174: | Line 134: | ||

| | | | ||

| C12 | | C12 | ||

| ISA_DAT_09 | | [[#PC104_Bus|ISA_DAT_09]]/[[#GPIO|Bank 8 IO 9]] | ||

| | | | ||

| D12 | | D12 | ||

| [[#GPIO|Bank 7 IO 9]] | | [[#GPIO|Bank 7 IO 9]] | ||

|- | |- | ||

| B20 | | B20 | ||

| N/A | | N/A | ||

| | | | ||

Revision as of 10:46, 16 December 2021

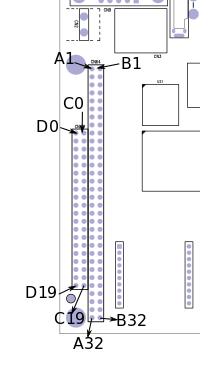

The PC104 connector consists of four rows of pins labelled A-D. The PC104 standard implements an ISA bus over these headers, but we also include the ability for almost all of the pins to be used as DIO.

| Pin | Description | Pin | Description | Pin | Description | Pin | Description | |||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| B32 | GND | A32 | GND | |||||||||||

| B31 | GND | A31 | ISA_ADD_00/Bank 9 IO 0 | |||||||||||

| B30 | ISA_14_3_MHZ [1] | A30 | ISA_ADD_01/Bank 9 IO 1 | |||||||||||

| B29 | +5V [2] | A29 | [[#PC104_Bus|ISA_ADD_02]/Bank 9 IO 2 | |||||||||||

| B28 | Bank 6 IO 1 | A28 | ISA_ADD_03/Bank 9 IO 3 | C19 | GND | D19 | GND | |||||||

| B27 | Bank 6 IO 2 | A27 | ISA_ADD_04/Bank 9 IO 4 | C18 | ISA_DAT_15/Bank 8 IO 15 | D18 | GND | |||||||

| B26 | Bank 6 IO 10 | A26 | ISA_ADD_05/Bank 9 IO 5 | C17 | ISA_DAT_14/Bank 8 IO 14 | D17 | Unused | |||||||

| B25 | FPGA IRQ 13 | A25 | ISA_ADD_06/Bank 9 IO 6 | C16 | ISA_DAT_13/Bank 8 IO 13 | D16 | +5V [2] | |||||||

| B24 | GND | A24 | ISA_ADD_07/Bank 9 IO 7 | C15 | ISA_DAT_12/Bank 8 IO 12 | D15 | Bank 7 IO 12 | |||||||

| B23 | FPGA IRQ 14 | A23 | ISA_ADD_08/Bank 9 IO 8 | C14 | ISA_DAT_11/Bank 8 IO 11 | D14 | Bank 7 IO 11 | |||||||

| B22 | FPGA IRQ 15 | A22 | [[#PC104_Bus|ISA_ADD_09 | Bank 9 IO 9 | C13 | ISA_DAT_10/Bank 8 IO 10 | D13 | Bank 7 IO 10 | ||||||

| B21 | FPGA IRQ 16 | A21 | ISA_ADD_10 | Bank 9 IO 10 | C12 | ISA_DAT_09/Bank 8 IO 9 | D12 | Bank 7 IO 9 | ||||||

| B20 | N/A | A20 | ISA_ADD_11 | Bank 9 IO 11 | C11 | ISA_DAT_08 | Bank 8 IO 8 | D11 | ISA_DRQ5 | Bank 7 IO 8 | ||||

| B19 | ISA_REFRESH | Bank 6 IO 6 | A19 | ISA_ADD_12 | Bank 9 IO 12 | C10 | Unused | N/A | D10 | ISA_DACK5 | Bank 7 IO 7 | |||

| B18 | ISA_DRQ1 | Bank 6 IO 7 | A18 | ISA_ADD_13 | Bank 9 IO 13 | C09 | Unused | N/A | D09 | ISA_DRQ0 | Bank 7 IO 6 | |||

| B17 | ISA_DACK1 | Bank 6 IO 8 | A17 | ISA_ADD_14 | Bank 9 IO 14 | C08 | Unused | N/A | D08 | ISA_DACK0 | Bank 7 IO 5 | |||

| B16 | ISA_DRQ3 | Bank 6 IO 12 | A16 | ISA_ADD_15 | Bank 9 IO 15 | C07 | Unused | N/A | D07 | ISA_IRQ14 | Bank 7 IO 4 | |||

| B15 | ISA_DACK3 | Bank 6 IO 13 | A15 | ISA_ADD_16 | Bank 10 IO 0 | C06 | Unused | N/A | D06 | ISA_IRQ15 | Bank 7 IO 3 | |||

| B14 | ISA_IOR | Bank 10 IO 4 | A14 | ISA_ADD_17 | Bank 10 IO 1 | C05 | N/A | Unused | D05 | ISA_IRQ12 | Bank 7 IO 2 | |||

| B13 | ISA_IOW | Bank 10 IO 5 | A13 | ISA_ADD_18 | Bank 10 IO 2 | C04 | Unused | N/A | D04 | ISA_IRQ11 | Bank 7 IO 1 | |||

| B12 | ISA_MEMR | Bank 10 IO 6 | A12 | ISA_ADD_19 | Bank 10 IO 3 | C03 | Unused | N/A | D03 | ISA_IRQ10 | Bank 7 IO 0 | |||

| B11 | ISA_MEMW | Bank 10 IO 7 | A11 | ISA_AEN | Bank 6 IO 0 | C02 | Unused | N/A | D02 | ISA_IO16 | Bank 10 IO 9 | |||

| B10 | GND | N/A | A10 | ISA_IORDY | Bank 6 IO 5 | C01 | Unused | N/A | D01 | ISA_MEM16 | Bank 10 IO 8 | |||

| B09 | +12V | 8V_48V [3] | A09 | ISA_DAT_00 | Bank 8 IO 0 | C00 | GND | N/A | D00 | GND | N/A | |||

| B08 | ISA_ENDX | Bank 6 IO 3 | A08 | ISA_DAT_01 | Bank 8 IO 1 | |||||||||

| B07 | Unused | N/A | A07 | ISA_DAT_03 | Bank 8 IO 3 | |||||||||

| B06 | ISA_DRQ2 | Bank 6 IO 9 | A06 | ISA_DAT_04 | Bank 8 IO 4 | |||||||||

| B05 | 3.3V [4] | N/A | A05 | ISA_DAT_05 | Bank 8 IO 5 | |||||||||

| B04 | ISA_IRQ9 | FPGA IRQ 17 | A04 | ISA_DAT_02 | Bank 8 IO 2 | |||||||||

| B03 | +5V [2] | N/A | A03 | ISA_DAT_06 | Bank 8 IO 6 | |||||||||

| B02 | ISA_RESET | Bank 2 IO 7 [5] | A02 | ISA_DAT_07 | Bank 8 IO 7 | |||||||||

| B01 | GND | N/A | A01 | ISA_IOCHK | Bank 2 IO 8 | |||||||||

- ↑ Outputs a continuous 14.318180 MHz clock

- ↑ 2.0 2.1 2.2 Powering the system from PC104 5V prevents the Board's low power sleep mode from functioning.

- ↑ This pin can be used to supply power to the board through the switching regulator.

- ↑ The PC104 standard uses -5V here. If a third party device is used that might use this rail, FB17 should be removed.

- ↑ This is automatically controlled by the ts-pc104 driver