TS-752: Difference between revisions

No edit summary |

No edit summary |

||

| Line 15: | Line 15: | ||

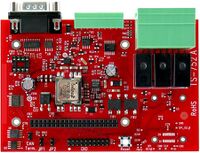

The TS-752 demonstrates the flexibility of a Technologic Systems SoM by connecting FPGA driven IO pins to relays, buffered digital inputs, buffered digital outputs, and RS-485 drivers. It also provides an RS-232 driver for the serial console. A TS-ENC750 with a TS-7500 or TS-7550 can provide a complete solution for many embedded applications. | The TS-752 demonstrates the flexibility of a Technologic Systems SoM by connecting FPGA driven IO pins to relays, buffered digital inputs, buffered digital outputs, and RS-485 drivers. It also provides an RS-232 driver for the serial console. A TS-ENC750 with a TS-7500 or TS-7550 can provide a complete solution for many embedded applications. | ||

= Host-board Recovery = | == Host-board Recovery == | ||

Although it is easy to get a [[TS-7500]] board into an unbootable state during development if you botch a modification, it is equally easy to use the TS-752 to recover the default startup. To do so, place the JP2 jumper on the TS-752 and reset the board. In approximately 3 seconds, the board will have fastbooted to the TS-752 flash and present a shell prompt. To recover the default initrd and linuxrc, enter the command "spisave", remove the JP2 jumper, and reboot back to a restored to factory default configuration. The procedure is identical on the [[TS-7550]] except you use the "nandsave" command since the TS-7550 has no SPI flash onboard. | Although it is easy to get a [[TS-7500]] board into an unbootable state during development if you botch a modification, it is equally easy to use the TS-752 to recover the default startup. To do so, place the JP2 jumper on the TS-752 and reset the board. In approximately 3 seconds, the board will have fastbooted to the TS-752 flash and present a shell prompt. To recover the default initrd and linuxrc, enter the command "spisave", remove the JP2 jumper, and reboot back to a restored to factory default configuration. The procedure is identical on the [[TS-7550]] except you use the "nandsave" command since the TS-7550 has no SPI flash onboard. | ||

== Relays == | |||

The TS-752 features 3 SPDT relays that the user can toggle through DIO. You can drive these DIO high or low to toggle the relays, or use the ts.subr file which lets you set a 3 bit value to control the relays. | |||

The PCH-105D2H relay is normally open, closes in 10ms, and opens in 5ms. A very safe assumption would be that it will switch after 20ms. | |||

<source lang=bash> | |||

# if you are in debian | |||

. /initrd/ts7500.subr | |||

# or if you are in initrd (may already be sourced) | |||

. /ts7500.subr | |||

# Disable all relays | |||

setrelay 0x0 | |||

# Enable all relays | |||

setrelay 0x7 | |||

</source> | |||

= Connectors = | |||

== DB9 Port == | |||

=== Diagram === | |||

============= | |||

\\1 2 3 4 5// | |||

\\6 7 8 9// | |||

========= | |||

=== Pinout === | |||

{| class="wikitable" | |||

|- | |||

! Pin # | |||

! Name | |||

! Function | |||

|- | |||

| 1 | |||

| 485_X+ | |||

| | |||

|- | |||

| 2 | |||

| CONSOLE_RXD | |||

| | |||

|- | |||

| 3 | |||

| CONSOLE_TXD | |||

| | |||

|- | |||

| 4 | |||

| NC | |||

| | |||

|- | |||

| 5 | |||

| GND | |||

| Ground | |||

|- | |||

| 6 | |||

| 485_X+ | |||

| | |||

|- | |||

| 7 | |||

| DIO_5_TXD | |||

| | |||

|- | |||

| 8 | |||

| DIO6_RXD2 | |||

| | |||

|- | |||

| 9 | |||

| NC | |||

| | |||

|} | |||

== 40 Pin Header == | |||

Note that 4 pins on the TS-7500 or TS-7550 will hang off. These include JTAG_DOUT, JTAG_TMS, JTAG_CLK, and JTAG_DIN. These are only needed for factory programming only. | |||

=== Diagram === | |||

_______ | |||

|01 | 02| | |||

|03 | 04| | |||

|05 | 06| | |||

|07 | 08| | |||

|09 | 10| | |||

|11 | 12| | |||

|13 | 14| | |||

|15 | 16| | |||

|17 | 18| | |||

|19 | 20| | |||

|21 | 22| | |||

|23 | 24| | |||

|25 | 26| | |||

|27 | 28| | |||

|29 | 30| | |||

|31 | 32| | |||

|33 | 34| | |||

|35 | 36| | |||

|37 | 38| | |||

|39 | 40| | |||

--------- | |||

=== Pinout === | |||

{| class="wikitable" | |||

|- | |||

! Pin # | |||

! Name | |||

! Function | |||

|- | |||

| 1 | |||

| DIO_05 / Mode2 | |||

| Used to toggle boot device (SD / offboard flash) | |||

|- | |||

| 2 | |||

| DIO_06 | |||

| XUART0_RX | |||

|- | |||

| 3 | |||

| DIO_07 | |||

| Console TX | |||

|- | |||

| 4 | |||

| DIO_08 | |||

| Console RX | |||

|- | |||

| 5 | |||

| DIO_09 | |||

| #RESET - drive high to reset the board | |||

|- | |||

| 6 | |||

| 3.3V | |||

| | |||

|- | |||

| 7 | |||

| DIO_11 / CS# | |||

| SPI CS# | |||

|- | |||

| 8 | |||

| DIO_12 | |||

| SPI MISO | |||

|- | |||

| 9 | |||

| DIO_13 | |||

| SPI MOSI | |||

|- | |||

| 10 | |||

| DIO_14 | |||

| SPI CLK | |||

|- | |||

| 11 | |||

| 5V | |||

| | |||

|- | |||

| 12 | |||

| GND | |||

| | |||

|- | |||

| 13 | |||

| DIO_17 | |||

| SCL | |||

|- | |||

| 14 | |||

| DIO_18 | |||

| SDA | |||

|- | |||

| 15 | |||

| DIO_19 | |||

| 485_TXD | |||

|- | |||

| 16 | |||

| DIO_20 | |||

| 485_RXD | |||

|- | |||

| 17 | |||

| DIO_21 | |||

| XUART2 TX | |||

|- | |||

| 18 | |||

| DIO_22 | |||

| XUART2 RX (TEMP_CS#) | |||

|- | |||

| 19 | |||

| DIO_23 | |||

| CAN_TXD | |||

|- | |||

| 20 | |||

| DIO_24 | |||

| CAN_RXD | |||

|- | |||

| 21 | |||

| DIO_25 | |||

| XUART4 TX | |||

|- | |||

| 22 | |||

| DIO_26 | |||

| BUF_IN8 | |||

|- | |||

| 23 | |||

| DIO_27 | |||

| 485_TXEN | |||

|- | |||

| 24 | |||

| DIO_28 | |||

| BUF_IN7 | |||

|- | |||

| 25 | |||

| DIO_29 | |||

| OUT_3 | |||

|- | |||

| 26 | |||

| DIO_30 | |||

| BUF_IN6 | |||

|- | |||

| 27 | |||

| DIO_31 | |||

| OUT_2 | |||

|- | |||

| 28 | |||

| DIO_32 | |||

| BUF_IN5 | |||

|- | |||

| 29 | |||

| DIO_33 | |||

| OUT_3 | |||

|- | |||

| 30 | |||

| DIO_34 | |||

| BUF_IN4 | |||

|- | |||

| 31 | |||

| DIO_35 | |||

| EN_RELAY1 | |||

|- | |||

| 32 | |||

| DIO_36 | |||

| BUF_IN3 | |||

|- | |||

| 33 | |||

| DIO_37 | |||

| EN_RELAY2 | |||

|- | |||

| 34 | |||

| DIO_38 | |||

| BUF_IN2 | |||

|- | |||

| 35 | |||

| DIO_39 | |||

| EN_RELAY1 | |||

|- | |||

| 36 | |||

| DIO_40 | |||

| BUF_IN1 | |||

|- | |||

| 37 | |||

| POE_RX | |||

| | |||

|- | |||

| 38 | |||

| POE_78 | |||

| | |||

|- | |||

| 39 | |||

| POE_45 | |||

| | |||

|- | |||

| 40 | |||

| POE_TX | |||

| | |||

|} | |||

== DIO Header == | |||

=== Diagram === | |||

_______ | |||

|01 | 02| | |||

|03 | 04| | |||

|05 | 06| | |||

|07 | 08| | |||

|09 | 10| | |||

|11 | 12| | |||

|13 | 14| | |||

|15 | 16| | |||

|17 | 18| | |||

|19 | 20| | |||

--------- | |||

=== Pinout === | |||

{| class="wikitable" | |||

|- | |||

! Pin # | |||

! Name | |||

! Function | |||

|- | |||

| 1 | |||

| 3.3V | |||

| | |||

|- | |||

| 2 | |||

| 485_TXD | |||

| | |||

|- | |||

| 3 | |||

| SDA | |||

| | |||

|- | |||

| 4 | |||

| SCL | |||

| | |||

|- | |||

| 5 | |||

| SPI MISO | |||

| | |||

|- | |||

| 6 | |||

| DIO_25 | |||

| | |||

|- | |||

| 7 | |||

| SPI_CLK | |||

| | |||

|- | |||

| 8 | |||

| 485_TXEN | |||

| | |||

|- | |||

| 9 | |||

| SPI_MOSI | |||

| | |||

|- | |||

| 10 | |||

| CAN_TXD | |||

| | |||

|- | |||

| 11 | |||

| OUT_3 | |||

| | |||

|- | |||

| 12 | |||

| CONSOLE_TXD | |||

| | |||

|- | |||

| 13 | |||

| REBOOT# | |||

| | |||

|- | |||

| 14 | |||

| DIO_21 | |||

| | |||

|- | |||

| 15 | |||

| DIO5_TXD2 | |||

| | |||

|- | |||

| 16 | |||

| OUT_2 | |||

| | |||

|- | |||

| 17 | |||

| NC | |||

| | |||

|- | |||

| 18 | |||

| OUT_1 | |||

| | |||

|- | |||

| 19 | |||

| 5V | |||

| | |||

|- | |||

| 20 | |||

| GND | |||

| | |||

|} | |||

== COM Ports == | |||

The XUART ports will be controlled with [[xuartctl]]. By default they will not have devices in /dev/. | |||

{| class="wikitable" | |||

|- | |||

! Name | |||

! Type | |||

! Location | |||

|- | |||

| XUART0 | |||

| RS232 | |||

| pins 7 (TX) and 8 (RX) of the [[#DB9 Port]] | |||

|- | |||

| XUART0 | |||

| TTL | |||

| pin 15 (TX Only) of the [[#DIO Header]] | |||

|- | |||

| XUART1 | |||

| RS485 | |||

| pins 1 (+) and 6 (-) of the [[#DB9 Port]] | |||

|- | |||

| XUART1 | |||

| TTL | |||

| pins 2 (TX Only) and 8 (TX Enable) of the [[#DIO Header]]. | |||

|- | |||

| XUART2 | |||

| TTL | |||

| pin 14 (TX Only) of the [[#DIO Header]] | |||

|- | |||

| XUART3 | |||

| TTL | |||

| pin 10 (TX Only) of the [[#DIO Header]] | |||

|- | |||

| XUART4 | |||

| TTL | |||

| pin 6 (TX Only) of the [[#DIO Header]] | |||

|- | |||

| XUART5 | |||

| TTL | |||

| pin 16 (TX Only) of the [[#DIO Header]] | |||

|- | |||

| XUART6 | |||

| TTL | |||

| pin 18 (TX Only) of the [[#DIO Header]] | |||

|- | |||

| XUART7 | |||

| N/A | |||

| N/A | |||

|} | |||

{{Note|XUART3 is not used when CAN is enabled}} | |||

Revision as of 12:31, 5 October 2011

| |

| Documentation | |

|---|---|

| Schematic | |

| Mechanical Drawing |

Overview

The TS-752 demonstrates the flexibility of a Technologic Systems SoM by connecting FPGA driven IO pins to relays, buffered digital inputs, buffered digital outputs, and RS-485 drivers. It also provides an RS-232 driver for the serial console. A TS-ENC750 with a TS-7500 or TS-7550 can provide a complete solution for many embedded applications.

Host-board Recovery

Although it is easy to get a TS-7500 board into an unbootable state during development if you botch a modification, it is equally easy to use the TS-752 to recover the default startup. To do so, place the JP2 jumper on the TS-752 and reset the board. In approximately 3 seconds, the board will have fastbooted to the TS-752 flash and present a shell prompt. To recover the default initrd and linuxrc, enter the command "spisave", remove the JP2 jumper, and reboot back to a restored to factory default configuration. The procedure is identical on the TS-7550 except you use the "nandsave" command since the TS-7550 has no SPI flash onboard.

Relays

The TS-752 features 3 SPDT relays that the user can toggle through DIO. You can drive these DIO high or low to toggle the relays, or use the ts.subr file which lets you set a 3 bit value to control the relays.

The PCH-105D2H relay is normally open, closes in 10ms, and opens in 5ms. A very safe assumption would be that it will switch after 20ms.

# if you are in debian

. /initrd/ts7500.subr

# or if you are in initrd (may already be sourced)

. /ts7500.subr

# Disable all relays

setrelay 0x0

# Enable all relays

setrelay 0x7

Connectors

DB9 Port

Diagram

============= \\1 2 3 4 5// \\6 7 8 9// =========

Pinout

| Pin # | Name | Function |

|---|---|---|

| 1 | 485_X+ | |

| 2 | CONSOLE_RXD | |

| 3 | CONSOLE_TXD | |

| 4 | NC | |

| 5 | GND | Ground |

| 6 | 485_X+ | |

| 7 | DIO_5_TXD | |

| 8 | DIO6_RXD2 | |

| 9 | NC |

40 Pin Header

Note that 4 pins on the TS-7500 or TS-7550 will hang off. These include JTAG_DOUT, JTAG_TMS, JTAG_CLK, and JTAG_DIN. These are only needed for factory programming only.

Diagram

_______ |01 | 02| |03 | 04| |05 | 06| |07 | 08| |09 | 10| |11 | 12| |13 | 14| |15 | 16| |17 | 18| |19 | 20| |21 | 22| |23 | 24| |25 | 26| |27 | 28| |29 | 30| |31 | 32| |33 | 34| |35 | 36| |37 | 38| |39 | 40| ---------

Pinout

| Pin # | Name | Function |

|---|---|---|

| 1 | DIO_05 / Mode2 | Used to toggle boot device (SD / offboard flash) |

| 2 | DIO_06 | XUART0_RX |

| 3 | DIO_07 | Console TX |

| 4 | DIO_08 | Console RX |

| 5 | DIO_09 | #RESET - drive high to reset the board |

| 6 | 3.3V | |

| 7 | DIO_11 / CS# | SPI CS# |

| 8 | DIO_12 | SPI MISO |

| 9 | DIO_13 | SPI MOSI |

| 10 | DIO_14 | SPI CLK |

| 11 | 5V | |

| 12 | GND | |

| 13 | DIO_17 | SCL |

| 14 | DIO_18 | SDA |

| 15 | DIO_19 | 485_TXD |

| 16 | DIO_20 | 485_RXD |

| 17 | DIO_21 | XUART2 TX |

| 18 | DIO_22 | XUART2 RX (TEMP_CS#) |

| 19 | DIO_23 | CAN_TXD |

| 20 | DIO_24 | CAN_RXD |

| 21 | DIO_25 | XUART4 TX |

| 22 | DIO_26 | BUF_IN8 |

| 23 | DIO_27 | 485_TXEN |

| 24 | DIO_28 | BUF_IN7 |

| 25 | DIO_29 | OUT_3 |

| 26 | DIO_30 | BUF_IN6 |

| 27 | DIO_31 | OUT_2 |

| 28 | DIO_32 | BUF_IN5 |

| 29 | DIO_33 | OUT_3 |

| 30 | DIO_34 | BUF_IN4 |

| 31 | DIO_35 | EN_RELAY1 |

| 32 | DIO_36 | BUF_IN3 |

| 33 | DIO_37 | EN_RELAY2 |

| 34 | DIO_38 | BUF_IN2 |

| 35 | DIO_39 | EN_RELAY1 |

| 36 | DIO_40 | BUF_IN1 |

| 37 | POE_RX | |

| 38 | POE_78 | |

| 39 | POE_45 | |

| 40 | POE_TX |

DIO Header

Diagram

_______ |01 | 02| |03 | 04| |05 | 06| |07 | 08| |09 | 10| |11 | 12| |13 | 14| |15 | 16| |17 | 18| |19 | 20| ---------

Pinout

| Pin # | Name | Function |

|---|---|---|

| 1 | 3.3V | |

| 2 | 485_TXD | |

| 3 | SDA | |

| 4 | SCL | |

| 5 | SPI MISO | |

| 6 | DIO_25 | |

| 7 | SPI_CLK | |

| 8 | 485_TXEN | |

| 9 | SPI_MOSI | |

| 10 | CAN_TXD | |

| 11 | OUT_3 | |

| 12 | CONSOLE_TXD | |

| 13 | REBOOT# | |

| 14 | DIO_21 | |

| 15 | DIO5_TXD2 | |

| 16 | OUT_2 | |

| 17 | NC | |

| 18 | OUT_1 | |

| 19 | 5V | |

| 20 | GND |

COM Ports

The XUART ports will be controlled with xuartctl. By default they will not have devices in /dev/.

| Name | Type | Location |

|---|---|---|

| XUART0 | RS232 | pins 7 (TX) and 8 (RX) of the #DB9 Port |

| XUART0 | TTL | pin 15 (TX Only) of the #DIO Header |

| XUART1 | RS485 | pins 1 (+) and 6 (-) of the #DB9 Port |

| XUART1 | TTL | pins 2 (TX Only) and 8 (TX Enable) of the #DIO Header. |

| XUART2 | TTL | pin 14 (TX Only) of the #DIO Header |

| XUART3 | TTL | pin 10 (TX Only) of the #DIO Header |

| XUART4 | TTL | pin 6 (TX Only) of the #DIO Header |

| XUART5 | TTL | pin 16 (TX Only) of the #DIO Header |

| XUART6 | TTL | pin 18 (TX Only) of the #DIO Header |

| XUART7 | N/A | N/A |

| Note: | XUART3 is not used when CAN is enabled |