TS-8100 DIO header: Difference between revisions

From embeddedTS Manuals

No edit summary |

(Fixed dead self-reference link) |

||

| (4 intermediate revisions by 2 users not shown) | |||

| Line 1: | Line 1: | ||

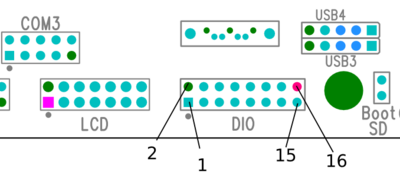

The TS-8100 includes a 2x8 0.1" pitch header with 8 DIO, I2C, and SPI. Most DIO on this header are rated for 3.3V and are not tolerant of 5V IO. The only exception is SPI_MOSI which is 5V tolerant. The DIO on this baseboard can be accessed by manipulating the [[# | The TS-8100 includes a 2x8 0.1" pitch header with 8 DIO, I2C, and SPI. Most DIO on this header are rated for 3.3V and are not tolerant of 5V IO. The only exception is SPI_MOSI which is 5V tolerant. The DIO on this baseboard can be accessed by manipulating the [[#TS-8100_Register_Map|TS-8100 Register Map]], or using [[#tsctl|tsctl]]. | ||

{| | {| | ||

| Line 86: | Line 80: | ||

| | | | ||

[[File:TS-8100-DIO.png|400px]] | |||

| | |||

|} | |} | ||

Latest revision as of 16:35, 9 July 2015

The TS-8100 includes a 2x8 0.1" pitch header with 8 DIO, I2C, and SPI. Most DIO on this header are rated for 3.3V and are not tolerant of 5V IO. The only exception is SPI_MOSI which is 5V tolerant. The DIO on this baseboard can be accessed by manipulating the TS-8100 Register Map, or using tsctl.

| Pinout | Header | |||||||||||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|