TS-8554-4400

| WARNING: | This manual is incomplete and is subject to change without notice while the TS-4400 and associated companion products are in development. |

| Product Page | |

| Documentation | |

|---|---|

| Processor | |

| 300 MHz | |

| Vortex86EX | |

| X86 Architecture | |

| Processor Page |

Overview

Getting Started

Connect USB Console

Powering up

Boot Sequence

BIOS

Technologic Systems uses a combination of Coreboot and SeaBIOS provided from the CPU manufacturer to bootstrap into FreeDOS. Unlike many BIOS solutions, this system has no peripheral settings that require customization, allowing the downstream developer to move more directly into product development.

Backup / Restore

Creating A Backup or Production Image

Restoring An Image

Cross Compiling and Development

Accessing The FPGA

FreeDOS Development

FreeRTOS Development

Features

Battery Backed RTC

CN1/CN2

| Odd Pins | 4400 CN1 Odd | 8554 CN1 Odd | even pins | 4400 CN1 Even | 8554 CN1 Even | Odd pins | 4400 CN2 Odd | 8554 CN2 Odd | even pins | 4400 CN2 Even | 8554 CN2 Even |

|---|---|---|---|---|---|---|---|---|---|---|---|

| 1 | FLASH_SEL_1 | FLASH_SEL_1 | 2 | 4400_REBOOT# | EXT_RESET# not used | 1 | ETH_RX_P | MDI0_P | 2 | ETH_ACT_LED | ETH_ACT_LED |

| 3 | 4 | EN_USB_HOST_5V | EN_AN_5V | 3 | ETH_RX_M | MDI0_M | 4 | ETH_RIGHT_LED | VORTEX_GP80 | ||

| 5 | FLASH_SEL_2 | FLASH_SEL_2 | 6 | CPU_SPI_MISO | CPU_SPI_MISO | 5 | 1.8V | ETH_CT | 6 | RED_LED# | RED_LED# |

| 7 | 8 | CPU_SPI_MOSI | CPU_SPI_MOSI | 7 | ETH_TX_P | MDI1_P | 8 | GREEN_LED# | GREEN_LED# | ||

| 9 | OFF_BD_RESET# | OFF_BD_RESET# | 10 | CPU_SPI_CLK | CPU_SPI_CLK | 9 | ETH_TX_M | MDI1_M | 10 | KB_CLK | KB_CLK |

| 11 | SILAB_CLK | 4400_SILAB_CLK | 12 | 11 | 1.8V | ETH_CT | 12 | KB_DAT | KB_DAT | ||

| 13 | SILAB_DAT | 4400_SILAB_DATA | 14 | FPGA_SPI_CLK | FPGA_SPI_CLK | 13 | 3.3V | SBC_3.3V | 14 | GND | GND |

| 15 | MAIN_5V | SBC_5V | 16 | MAIN_5V | SBC_5V | 15 | GND | GND | 16 | HDA_BCLK | |

| 17 | NO_CHRG_JMP# | VORTEX_GP84 | 18 | FPGA_SPI_MOSI | FPGA_SPI_MOSI | 17 | 18 | HDA_SYNC | |||

| 19 | U_BOOT_JMP# | VORTEX_GP82 | 20 | FPGA_SPI_MISO | FPGA_SPI_MISO | 19 | 20 | HDA_SDO | |||

| 21 | DIO_44 | ISA_BCLK | 22 | FORCE_PWR_ON# | FORCE_SBC_5V_ON# not used | 21 | GND | GND | 22 | HDA_SDI | |

| 23 | DIO_40 | MIKRO_SPI_CLK | 24 | DIO_41 | ISA_ADD_08 | 23 | 24 | HDA_RST# | |||

| 25 | DIO_47 | MIKRO_SPI_MOSI | 26 | DIO_42 | ISA_ADD_09 | 25 | 26 | GND | GND | ||

| 27 | DIO_48 | MIKRO_SPI_MISO | 28 | DIO_60 | Vortex_GP81 and FPGA | 27 | 28 | I2C_CLK | I2C_CLK | ||

| 29 | MAIN_5V | SBC_5V | 30 | DIO_61 | PC104_IRQ5 | 29 | USB_HOST1_M | USB_HOST_M | 30 | I2C_DAT | I2C_DAT |

| 31 | DIO_49 | MIKRO_SPI_CS# | 32 | DIO_62 | PC104_IRQ6 | 31 | USB_HOST1_P | USB_HOST_P | 32 | SPEAKER | SPKR |

| 33 | DIO_50 | MIKRO_PWM | 34 | DIO_63 | PC104_IRQ7 | 33 | GND | GND | 34 | DAC_3 | DAC_D |

| 35 | DIO_51 | MIKRO_INT | 36 | V_BAT | V_BAT | 35 | USB_HOST2_M | USB_HOST2_M | 36 | CPU_JTAG_TDI | JTAG |

| 37 | DIO_45 | MIKRO_RESET# | 38 | DIO_64 | DIO_5 | 37 | USB_HOST2_P | USB_HOST2_P | 38 | CPU_JTAG_TDO | JTAG |

| 39 | DIO_46 | WIFI_MISO | 40 | DIO_65 | DIO_7 | 39 | 3.3V | SBC_3.3V | 40 | ||

| 41 | DIO_52 | WIFI_32KHZ | 42 | DIO_66 | DIO_9 | 41 | SATA_TX_P | SATA_TX_P | 42 | CPU_JTAG_TCK | JTAG |

| 43 | DIO_53 | WIFI_CTS | 44 | DIO_67 | DIO_11 | 43 | SATA_TX_M | SATA_TX_M | 44 | GND | GND |

| 45 | DIO_54 | LCD_DATA_LK | 46 | DIO_68 | COM1_CTS_3V | 45 | GND | GND | 46 | CPU_FLASH_CS# | CPU_FLASH_CS# |

| 47 | MAIN_5V | 5V_A | 48 | DIO_43 | DIO_SPI_MISO | 47 | SATA_RX_M | SATA_RX_M | 48 | CPU_SPI_CS# | CPU_SPI_CS# |

| 49 | DIO_55 | WIFI_MOSI | 50 | 49 | SATA_RX_P | SATA_RX_P | 50 | GND2? | GND | ||

| 51 | DIO_56 | EN_NIM_USB# | 52 | BOOT_MODE_0 | VORTEX_GP35 | 51 | GND | GND | 52 | AN0 | AN_0 |

| 53 | DIO_57 | WIFI_CLK | 54 | 53 | 4400_PRESENT# | 4400_PRESENT# | 54 | CPU_JTAG_TMS | JTAG | ||

| 55 | DIO_58 | WIFI_CS# | 56 | 55 | 4400_REBOOT# | 4400_REBOOT# | 56 | AN_1 | AN_1 | ||

| 57 | DIO_59 | PROT_0_CLK | 58 | DIO_39 | DIO_SPI_MOSI | 57 | SSD_PRESENT | VORTEX_GP83 | 58 | AN_2 | AN_2 |

| 59 | DIO_16 | PORT_1_CLK | 60 | DIO_38 | DIO_SPI_CLK | 59 | FPGA_SPI_CS# | FPGA_SPI_CS# | 60 | AN_3 | AN_3 |

| 61 | DIO_15 | ISA_IOW# | 62 | GND | GND | 61 | FPGA_FLASH_CS# | FPGA_FLASH_CS# | 62 | AN_4 | AN_4 |

| 63 | DIO_14 | ISA_IOR# | 64 | DIO_37 | ISA_DATA_15 | 63 | 1.8V | SBC_1.8IV | 64 | AN_5 | AN_5 |

| 65 | DIO_13 | WIFI_IRQ# | 66 | DIO_36 | ISA_DATA_14 | 65 | SPI_OB_CS# | SBC_SPI_CS# | 66 | AN_6 | AN_6 |

| 67 | DIO_12 | TX_EN_485 | 68 | DIO_35 | ISA_DATA_13 | 67 | SPI_OB_MOSI | SBC_SPI_MOSI | 68 | AN_7 | AN_7 |

| 69 | DIO_11 | IO16# | 70 | DIO_34 | ISA_DATA_12 | 69 | SPI_OB_MISO | SBC_SPI_MISO | 70 | DAC_0 | DAC_A |

| 71 | DIO_10 | WIFI_TXD | 72 | DIO_33 | ISA_DATA_11 | 71 | SPI_OB_CLK | SBC_SPI_CLK | 72 | DAC_1 | DAC_B |

| 73 | DIO_09 | PUSH_SW# | 74 | DIO_32 | ISA_DATA_10 | 73 | GND | GND | 74 | ||

| 75 | GND | GND | 76 | DIO_31 | ISA_DATA_09 | 75 | SUP_CAP_PLUS | SUP_CAP_PLUS | 76 | ||

| 77 | DIO_08 | EN_NIMBEL_3.3V | 78 | DIO_30 | ISA_DATA_08 | 77 | SUP_CAP_PLUS | SUP_CAP_PLUS | 78 | UART_0_TXD | 485_TXD |

| 79 | DIO_07 | EN_NIMBEL_4V | 80 | DIO_29 | ISA_DATA_07 | 79 | 80 | UART_0_RXD | 485_RXD_3V | ||

| 81 | DIO_06 | ISA_RESET | 82 | DIO_28 | ISA_DATA_06 | 81 | SUP_CAP_PLUS | SUP_CAP_PLUS | 82 | UART_1_TXD | UART1 TXD |

| 83 | DIO_05 | BD_ID_DATA | 84 | DIO_27 | ISA_DATA_05 | 83 | SUP_CAP_PLUS | SUP_CAP_PLUS | 84 | UART_1_RXD | UART1_RXD_3V |

| 85 | DIO_04 | WIFI_RXD | 86 | DIO_26 | ISA_DATA_04 | 85 | GND | GND | 86 | UART_2_TXD | UART2_TXD |

| 87 | DIO_03 | ISA_14.3MHZ | 88 | DIO_25 | ISA_DATA_03 | 87 | AN_SUP_CAP_1 | SUP_CAP_JUNC | 88 | UART_2_RXD | UART2_RXD_3V |

| 89 | DIO_02 | BUF_LCD_03 | 90 | DIO_24 | ISA_DATA_02 | 89 | SUP_CAP_DRIVE | BAL_DRIVE | 90 | UART_3_TXD | UART3_TXD |

| 91 | DIO_01 | BUD_LCD_05 | 92 | DIO_23 | ISA_DATA_01 | 91 | DAC_2 | DAC_C | 92 | UART_3_RXD | UART3_RXD_3V |

| 93 | DIO_00 | BUF_LCD_06 | 94 | DIO_22 | ISA_DATA_00 | 93 | 94 | UART_4_TXD | NIMBEL_TXD | ||

| 95 | GND | GND | 96 | DIO_21 | ISA_ALE | 95 | 96 | UART_4_RXD | NIMBEL_RXD | ||

| 97 | DIO_17 | ISA_IORDY | 98 | DIO_20 | ISA_DIR | 97 | CAN_TXD | CAN_TXD | 98 | UART_5_TXD | MIKRO_TXD |

| 99 | DIO_18 | ISA_BHE# | 100 | DIO_19 | ISA_CS# | 99 | CAN_RXD | CAN_RXD_3V | 100 | UART_5_RXD | MIKRO_RXD |

CPU

| DIO_# | FUNCTION | TS-8554 PIN | CN1 LOCATION |

|---|---|---|---|

| 0 | GPIO | BUF_LCD_06 | 93 |

| 1 | GPIO | BUF_LCD_05 | 91 |

| 2 | GPIO | BUF_LCD_03 | 89 |

| 3 | GPIO | ISA_14.3 MHZ | 87 |

| 4 | GPIO | WIFI_RXD | 85 |

| 5 | GPIO | BD_ID_DATA | 83 |

| 6 | GPIO | ISA_RESET | 81 |

| 7 | GPIO | EN_NIMBEL_4V | 79 |

| 8 | GPIO | EN_NIMBEL_3.3V | 77 |

| 9 | GPIO | PUSH_SW# | 73 |

| 10 | GPIO | WIFI_TXD | 71 |

| 11 | GPIO | IO16# | 69 |

| 12 | GPIO | TX_EN_485 | 67 |

| 13 | GPIO | WIFI_IRQ# | 65 |

| 14 | GPIO | ISA_IOR# | 63 |

| 15 | GPIO | ISA_IOW# | 61 |

| 16 | GPIO | PORT_1_CLK | 59 |

| 17 | GPIO | ISA_IORDY | 97 |

| 18 | GPIO | ISA_BHE# | 99 |

| 19 | GPIO | ISA_CS# | 100 |

| 20 | GPIO | ISA_DIR | 98 |

| 21 | GPIO | ISA_ALE | 96 |

| 22 | GPIO | ISA_DATA_00 | 94 |

| 23 | GPIO | ISA_DATA_01 | 92 |

| 24 | GPIO | ISA_DATA_02 | 90 |

| 25 | GPIO | ISA_DATA_03 | 88 |

| 26 | GPIO | ISA_DATA_04 | 86 |

| 27 | GPIO | ISA_DATA_05 | 84 |

| 28 | GPIO | ISA_DATA_06 | 82 |

| 29 | GPIO | ISA_DATA_07 | 80 |

| 30 | GPIO | ISA_DATA_08 | 78 |

| 31 | GPIO | ISA_DATA_09 | 76 |

| 32 | GPIO | ISA_DATA_10 | 74 |

| 33 | GPIO | ISA_DATA_11 | 72 |

| 34 | GPIO | ISA_DATA_12 | 70 |

| 35 | GPIO | ISA_DATA_13 | 68 |

| 36 | GPIO | ISA_DATA_14 | 66 |

| 37 | GPIO | ISA_DATA_15 | 64 |

| 38 | GPIO | DIO_SPI_CLK | 60 |

| 39 | GPIO | DIO_SPI_MOSI | 58 |

| 40 | GPIO | MIKRO_SPI_CLK | 23 |

| 41 | GPIO | ISA_ADD_08 | 24 |

| 42 | GPIO | ISA_ADD_09 | 26 |

| 43 | GPIO | DIO_SPI_MISO | 48 |

| 44 | GPIO | ISA_BCLK | 21 |

| 45 | GPIO | MIKRO_RESET# | 37 |

| 46 | GPIO | WIFI_MISO | 39 |

| 47 | GPIO | MIKRO_SPI_MOSI | 25 |

| 48 | GPIO | MIKRO_SPI_MISO | 27 |

| 49 | GPIO | MIKRO_SPI_CS# | 31 |

| 50 | GPIO | MIKRO_PWM | 33 |

| 51 | GPIO | MIKRO_INT | 35 |

| 52 | GPIO | WIFI_32KHZ | 41 |

| 53 | GPIO | WIFI_CTS | 43 |

| 54 | GPIO | LCD_DATA_LK | 45 |

| 55 | GPIO | WIFI_MOSI | 49 |

| 56 | GPIO | EN_NIM_USB# | 51 |

| 57 | GPIO | WIFI_CLK | 53 |

| 58 | GPIO | WIFI_CS# | 55 |

| 59 | GPIO | PORT_0_CLK | 57 |

| 60 | GPIO | vortex_gp81 & fpga | 28 |

| 61 | GPIO | PC104_IRQ5 | 30 |

| 62 | GPIO | PC104_IRQ6 | 32 |

| 63 | GPIO | PC104_IRQ7 | 34 |

| 64 | GPIO | DIO_5 | 38 |

| 65 | GPIO | DIO_7 | 40 |

| 66 | GPIO | DIO_9 | 42 |

| 67 | GPIO | DIO_11 | 44 |

| 68 | GPIO | COM1_CTS_3V | 46 |

ADC

Ethernet Port

FPGA

FPGA Registers

FPGA Syscon

Interrupts

LEDs

Sleep

SPI

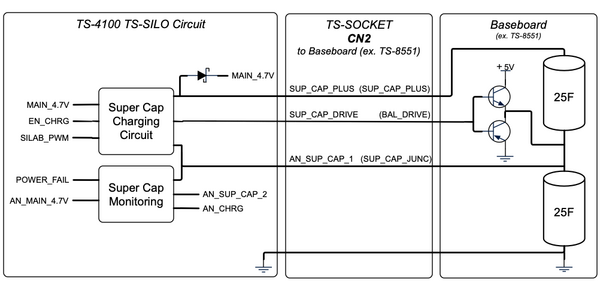

TS-SILO Supercapacitors

XXX TODO: This section needs a generic graphic or one dedicated to the TS-4400.

UARTs

USB

XXX TODO: Is this a duplicate of section 7's USB section?

Watchdog

Specifications

Power Input Specifications

Power Consumption

Power Rails

MicroSD Connector

MicroUSB Connector

Power Connectors

USB Ports

Revisions and Changes

FPGA Changelog

Microcontroller Changelog

PCB Revisions

Software Images

Product Notes

FCC Advisory

This equipment generates, uses, and can radiate radio frequency energy and if not installed and used properly (that is, in strict accordance with the manufacturer's instructions), may cause interference to radio and television reception. It has been type tested and found to comply with the limits for a Class A digital device in accordance with the specifications in Part 15 of FCC Rules, which are designed to provide reasonable protection against such interference when operated in a commercial environment. Operation of this equipment in a residential area is likely to cause interference, in which case the owner will be required to correct the interference at his own expense.

If this equipment does cause interference, which can be determined by turning the unit on and off, the user is encouraged to try the following measures to correct the interference:

Reorient the receiving antenna. Relocate the unit with respect to the receiver. Plug the unit into a different outlet so that the unit and receiver are on different branch circuits. Ensure that mounting screws and connector attachment screws are tightly secured. Ensure that good quality, shielded, and grounded cables are used for all data communications. If necessary, the user should consult the dealer or an experienced radio/television technician for additional suggestions. The following booklets prepared by the Federal Communications Commission (FCC) may also prove helpful:

How to Identify and Resolve Radio-TV Interference Problems (Stock No. 004-000-000345-4) Interface Handbook (Stock No. 004-000-004505-7) These booklets may be purchased from the Superintendent of Documents, U.S. Government Printing Office, Washington, DC 20402.

Limited Warranty

See our Terms and Conditions for more details.