TS-8820-4720: Difference between revisions

(→Booting: Added some information about what it should look like.) |

(added getting a console + options partially copied from or using ts-4710 content pages.) |

||

| Line 40: | Line 40: | ||

{{:Generic_Booting_TSBootROM}} | {{:Generic_Booting_TSBootROM}} | ||

== Getting a Console == | |||

=== Option 1: Telnet === | |||

{{:TS-4710 Telnet}} | |||

=== Option 2: Serial Console === | |||

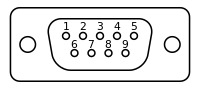

The console UART (ttyS0) is an RS232 UART at 115200 baud, 8n1 (8 data bits 1 stop bit), and no flow control. This appears at [[#DB9|Pin 2 (TX) and Pin 3 (RX)]]. | |||

{{:Console From Linux Workstation}} | |||

{{:Console from Windows Workstation}} | |||

= Features = | = Features = | ||

Revision as of 18:02, 6 March 2017

| WARNING: | This article is a work in progress. If you have questions about using the TS-8820-4720, please call our support team, or email support@embeddedarm.com. Thanks! |

| |

| Product Page | |

| Image Gallery | |

| Documentation | |

|---|---|

| Schematic | |

| Software Support | |

| TS-8820 source directory | |

| Dimensions (in enclosure) | |

| 6.35 inches (tall) by 7.714 inches (wide including DB9) by 1.14 inches (deep) |

Overview

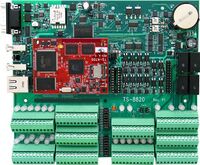

The TS-8820-BOX is a rugged, feature-rich TS-SOCKET based baseboard and System-on-Module (SoM) combination for industrial applications. The TS-8820-BOX is powered by the TS-4100, TS-4700, TS-4710, TS-4720 or TS-4800 System-on-Module devices. The TS-8820-BOX enclosure exposes all of the available I/O on rugged screw terminals while protecting the SoM and other sensitive electronics. The TS-8820-BOX a tough, durable, flexible, powerful, and affordable industrial process control platform.

Getting Started

A Linux PC is recommended for development, and will be assumed for this documentation. For users in Windows or OSX we recommend virtualizing a Linux PC. Most of our platforms run Debian and if there is no personal distribution preference this is what we recommend for ease of use.

Virtualization

Suggested Linux Distributions

It may be possible to develop using a Windows or OSX system, but this is not supported. Development will include accessing drives formatted for Linux and often Linux based tools.

Of particular importance, you will need these things:

- A desktop computer with an unrestricted internet connection.

- A wired Ethernet connection to the same local area network as the above desktop computer.

- A TS-8820-4720.

- A reliable 12-24 VDC power source.

- An RS232 serial crossover cable connected to the above Desktop computer.

- Download the ts8820ctl source code from the TS-8820 ftp directory.

Connecting Power

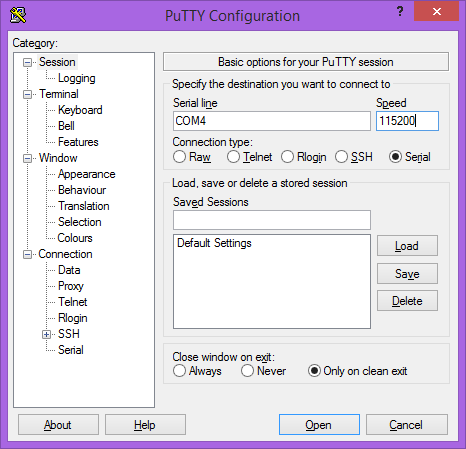

The TS-8820-4720 takes 12 to 24 VDC input on header P6. Connect ground to P6 pin 6 and + VDC to pin P6 pin 7. Note for applications with particularly strong current draw, P6 pins 8 and 9 can also be used for + VDC, and P6 pin 5 is also a safe GND connection.

Booting

The TS-4720 eMMC contains a bootable Linux image by default. The system will start up automatically when connected to power.

Once you have applied power to the baseboard, look for console output. The next section of the manual provides information on getting the console connected. The first output is from the bootrom:

>> TS-BOOTROM - built Jan 21 2013 16:17:55 >> Copyright (c) 2012, Technologic Systems . . Uncompressing Linux... done, booting the kernel. Booted in 0.66 s Type 'tshelp' for help #

The "Booting From" message will indicate your boot media. The 2 dots after indicate steps of the booting procedure. The first dot means the MBR was copied into memory and executed. The next dot indicates that the MBR executed and the kernel/initramfs were copied into memory and executed.

Getting a Console

Option 1: Telnet

If your system is configured with zeroconf support (Avahi, Bonjour, etc) you can simply connect to the TS-4710 with:

telnet ts4710-<last 6 characters of the MAC address>.local

# You will need to use your TS-4710 MAC address, but

# for example if you mac is 00:d0:69:01:02:03

telnet ts4710-010203.local

When the board first powers up it has two network interfaces. The first interface eth0 is configured to use IPv4LL, and eth0:0 is configured to use DHCP. The board broadcasts using multicast DNS advertising the _telnet._tcp service. You can use this to query all of the available TS-4710s on the network.

From Linux you can use the avahi commands to query for all telnet devices with:

avahi-browse _telnet._tcp

Which would return:

+ eth0 IPv4 TS-4710 console [4f47a5] Telnet Remote Terminal local + eth0 IPv4 TS-4710 console [4f471a] Telnet Remote Terminal local

This will show you the mac address you can use to resolve the board. In this case you can connect to either ts4710-4f47a5 or ts4710-4f47a5.

From Windows you can use Bonjour Print Services to get the dns-sd command. OSX also comes preinstalled with the same command. Once this is installed you can run:

dns-sd -B _telnet._tcp

Which will return:

Browsing for _telnet._tcp Timestamp A/R Flags if Domain Service Type Instance Name 10:27:57.078 Add 3 2 local. _telnet._tcp. TS-4710 console [4f47a5] 10:27:57.423 Add 3 2 local. _telnet._tcp. TS-4710 console [4f47a5]

This will show you the mac address you can use to resolve the board. In this case you can connect to either ts4710-4f47a5.local or ts4710-4f47a5.local.

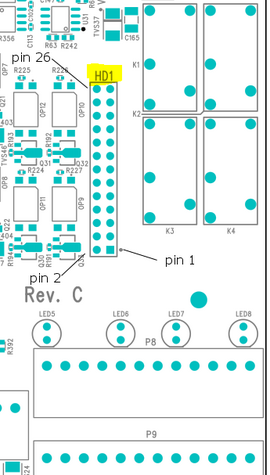

Option 2: Serial Console

The console UART (ttyS0) is an RS232 UART at 115200 baud, 8n1 (8 data bits 1 stop bit), and no flow control. This appears at Pin 2 (TX) and Pin 3 (RX).

Console from Linux

There are many serial terminal applications for Linux, three common used applications are picocom, screen, and minicom. These examples demonstrate all three applications and assume that the serial device is "/dev/ttyUSB0" which is common for USB adapters. Be sure to replace the serial device string with that of the device on your workstation.

picocom is a very small and simple client.

sudo picocom -b 115200 /dev/ttyUSB0

screen is a terminal multiplexer which happens to have serial support.

sudo screen /dev/ttyUSB0 115200

Or a very commonly used client is minicom which is quite powerful but requires some setup:

sudo minicom -s

- Navigate to 'serial port setup'

- Type "a" and change location of serial device to "/dev/ttyUSB0" then hit "enter"

- If needed, modify the settings to match this and hit "esc" when done:

E - Bps/Par/Bits : 115200 8N1

F - Hardware Flow Control : No

G - Software Flow Control : No

- Navigate to 'Save setup as dfl', hit "enter", and then "esc"

Console from Windows

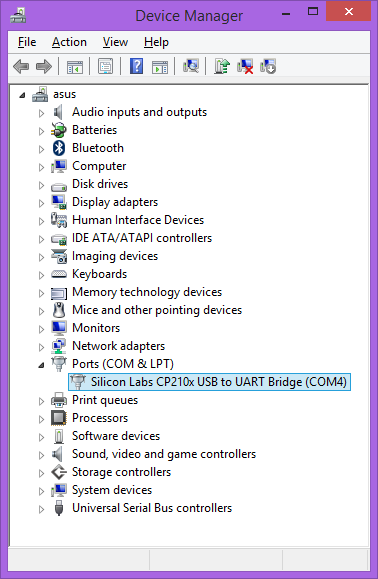

Putty is a small simple client available for download here. Open up Device Manager to determine your console port. See the putty configuration image for more details.

Features

TS-4720

The TS-4720 is a Computer On Module design in the TS-SOCKET family. The TS-4720 forms the computational heart of the TS-8820-4720 version of the TS-8820-BOX product.

See the TS-4720 page for functionality regarding the CPU, the CPU Module's FPGA, and Operating System.

|

Marvell PXA168 1066MHz Mohawk (ARMv5), eMMC |

FPGA

The TS-8820 is powered by a Lattice XP2 FPGA with 5000 LUTs. Many but not all of the features listed in chapter 5 are driven by FPGA logic. The hardware functionality described in this document is programmed in the FPGA at the factory by default. The TS-SOCKET System-on-Module (SoM) also has an FPGA, but when an FPGA is mentioned in this document it should be assumed that the TS-8820 FPGA is being discussed.

The SoM communicates with the TS-8820 FPGA using the MUXBUS, a simple address/data bus defined by embeddedTS and implemented in the SoM FPGA. TS-8820 application developers do not need to understand the full hardware stack that enables TS-8820 registers to be accessed in memory space. It is necessary to program the MUXBUS registers with values that work for the TS-8820. See ts8820ctl source code for an example.

For applications that require custom logic or interfaces, contact embeddedTS regarding custom FPGA customization. Sources for the The TS-8820 FPGA are also available via special arrangement with embeddedTS, contact sales@embeddedTS.com for more information.

Non-Volatile RAM

The TS-8820 provides 2MB of battery backed static RAM. The RAM is accessed through a 4KB memory window. After programming the SRAM page register, 16 bit reads or writes can be performed to any part of the page.

This can be accessed through ts8820ctl:

echo "test" | ts8820ctl -W 5

ts8820ctl -R 5

| Note: | The SRAM is not populated by default. See U16 to verify the presence on your board. If you require battery backed SRAM please contact us. |

Battery Socket

The coin cell battery is not required for normal TS-8820 operation. The battery provides backup power for the battery backed SRAM and for the real time clock located on the SoM. Without a battery, however, a loss of power will result in a loss of RTC time in the SoM and SRAM data on the TS-8820.

Digital Outputs

The TS-8820 offers 6 digital outputs. OUT1 through OUT4 are isolated and act as a solid state relay capable of switching up to 40 VDC at 1 A continuous draw. OUT5 and OUT6 are non-isolated, able to sink up to 1 A continuous current, and are 40 VDC tolerant.

The outputs can be controlled directly through the 'ts8820ctl' application. See "ts8820ctl.c" and "ts8820.c" for examples of how this writes to the TS-8820 registers.

With the 'ts8820ctl' application, all 6 outputs are manipulated in a single command. That is, a 6-bit value is passed as an argument, and that value is directly set to the outputs. For example, to set OUT5:

ts8820ctl --setdio=0x10

When an output is activated its associated LED indicator is enabled to provide visual feedback.

Isolated Outputs

Digital outputs OUT1 through OUT4 are isolated, each having their own positive and negative terminal. Each isolated output acts as a solid state relay allowing current to flow through the contacts only when it is activated. The isolated outputs are able to switch up to 40 VDC at 1 A continuous current draw. Isolated output terminals are made available on the P7 terminal block.

Non-Isolated Outputs

Digital outputs OUT5 and OUT6 are non-isolated, they rely on the main TS-8820 ground and only have a single contact. Each non-isolated output is a low side switch capable of sinking current when activated. The non-isolated outputs are capable of sinking 1 A continuous current with 40 V input voltage. Non-isolated input terminals appear on the P2 terminal block.

PWM

The TS-8820 has 6 PWM outputs. PWM channels 1 to 6 feed digital outputs 1 to 6 respectively when the PWM override bit is set for a given output.

For all 8 PWM channels, the PWM frequency is approximately (12207/(2^prescaler)) Hz, where the prescaler value is 3 bits wide. That is, a prescaler value of 0 through 7. The PWM duty cycle has 12 bits of resolution. If bit 12 of a PWM register is set, then the PWM output for that channel will be 100% high. Otherwise, the duty cycle setting is divided by 4096 to give the effective duty cycle.

To give OUT5 a ~3 kHZ 50% duty cycle PWM output using ts8820ctl, the following arguments would be used:

# -P sets the PWM frequency via a prescaler value to (12207/(2^VALUE))Hz.

# --mvolts= sets the PWM duty cycle percentage from a decimal scale of 0-10000

# --pwm= PWM channel to enable and modify

ts8820ctl --pwm=5 --mvolts=5000 -P 2

Digital Inputs

The TS-8820 offers 14 digital input pins. There are 8 isolated inputs that are 30 V tolerant. The 6 non-isolated inputs are 40 V tolerant.

The inputs can be polled directly through the ts8820ctl application. See ts8820ctl.c and ts8820.c for examples of how this reads from the TS-8820 registers.

With the ts8820ctl application, all 14 inputs can be read with a single command. A 14-bit value is returned in hex in a format that can be parsed easily by scripting languages. For example, the following output indicates that IN1 and IN3 are active:

ts8820ctl --getdio

dio=0x5

When an input is activated its associated LED indicator is enabled to provide visual feedback.

All inputs (isolated and non-isolated) are also accessible by reading the combined input register at 0x80008004, and are represented in a bitwise manner from bit 0 (input 1) through bit 13 (input 14).

Buffered Inputs

Digital inputs IN9 through IN14 are non-isolated, buffered, active low inputs. Each pin has a nominal threshold of 2.5 VDC, a 3.24 Kohm pull-up to 5 VDC, and are 40 VDC tolerant. Non-isolated inputs are located on the P2 terminal block.

Isolated Inputs

Digital inputs IN1 though IN8 are isolated, each having their own positive and negative terminal. In order to activate an input, a potential of at least 1.4 VDC and not more than 30 VDC must be generated across these terminals. Isolated input terminals are located on P1 and P7 terminal blocks.

Pulse Counters

Every input has its own wrap-around pulse count register. Wrap-around means that there is no "zero" function. The counter will count up to 65535 pulses and wrap to zero. For usage details please see the sample code below:

// ts8820 pulse counter demo

// c. Technologic Systems, Inc. 2017

// Written by Michael D Peters.

//

// Required materials:

// TS-8820

// TS-47xx

// 2 jumper wires about 10 inches long.

// 1 100k ohm leaded resistor

//

// Setup:

// Connect Relay 1's COM pin (P8 pin 2) to IN_14.

// Connect NC (P8 pin 3) to VIN using the 100K ohm resistor.

// Connect NO (P8 pin 1) to GND (any, P4 pin 12 works).

//

// This program toggles relay 1 and watches the pulse counter

// register for input 14, displaying rising edges coming from

// relay 1.

//

// Basically, the program provides a cycle count on the relay

// toggle. Expect "bounces" during the relay throw as

// the input pin will float to any noise during the relay's

// falling transition period.

#include <stdio.h>

#include <sys/mman.h>

#include <fcntl.h>

#include <stdint.h>

#define RELAY_REGISTER 0x10

#define PULSE_COUNTER_14 0x3a

enum TS8820_RELAYS {

RELAYS_OFF = 0x0000,

RELAY4 = 0X10,

RELAY3 = 0X40,

RELAY2 = 0X80,

RELAY1 = 0x100

};

int main(int argc, char* argv[])

{

int i, mem;

uint16_t *syscon;

uint16_t *baseboard;

// memory setup

mem=open("/dev/mem", O_RDWR|O_SYNC);

syscon = mmap(0, getpagesize(), PROT_READ|PROT_WRITE, MAP_SHARED, mem, 0x80004000);

baseboard = mmap(0, getpagesize(), PROT_WRITE|PROT_READ, MAP_SHARED, mem, 0x80008000);

// set muxbus speed to really slow (high delay).

syscon[0x4/2] = 0xf3ff;

// set dio direction to output for the relays.

syscon[0x18/2] = 0x1d0;

for(;;){ // forever loop starts here.

syscon[RELAY_REGISTER/2] = (uint16_t)RELAY1;

printf("RELAY1 is ON\n");

i = baseboard[PULSE_COUNTER_14/2];

printf("Pulse counter 14 at %d\n", i);

usleep(125000); // 1/8 second.

syscon[RELAY_REGISTER/2] = (uint16_t)RELAYS_OFF;

printf("Relays are OFF\n");

i = baseboard[PULSE_COUNTER_14/2];

printf("Pulse counter 14 at %d\n", i);

usleep(125000); // 1/8 second.

}

return 0;

}

ADC Channels

The TS-8820 offers 16 channels of single ended bi-polar ADC inputs. These ADC inputs are provided by two separate 8 channel ADC devices. Each ADC controller supports a selectable voltage (via GPIO from the SoM, see below) ranges of -5 V to +5 V as well as -10 V to +10 V. This means that each set of 8 channels can be set to different ranges. Each set of 8 channels are sampled simultaneously inside the ADC device.

All 16 ADC inputs are located on the P3, P4, and P5 terminal blocks. While each ADC has a pair of inputs, they are single ended ADC channels; all negative input terminals connect to the TS-8820 common ground.

Additionally, the ADC devices support a number of oversampling options, also controlled via GPIO from the SoM. Enabling oversampling has the effect of adding a digital filter function after the ADC. Increasing the oversampling ratio will decrease the effective sampling rate of the ADC but will increase the signal to noise ratio of each channel. The oversampling rate is shared between both ADC devices, that is, the rate can not be independently set per-device.

Setting the ADC voltage range:

| DIO | Val | Range |

|---|---|---|

| CN2_56 | 1 | -10 V to +10 V |

| CN2_56 | 0 | -5 V to +5 V |

| DIO | Val | Range |

|---|---|---|

| CN2_58 | 1 | -10 V to +10 V |

| CN2_58 | 0 | -5 V to +5 V |

Setting the oversampling rate:

| CN2_64 | CN2_62 | CN2_60 | OS Rate |

|---|---|---|---|

| 0 | 0 | 0 | N/A |

| 0 | 0 | 1 | 2 |

| 0 | 1 | 0 | 4 |

| 0 | 1 | 1 | 8 |

| 1 | 0 | 0 | 16 |

| 1 | 0 | 1 | 32 |

| 1 | 1 | 0 | 64 |

| 1 | 1 | 1 | Invalid |

| Note: | SoM GPIO pins will usually start as inputs with pull up resistors. Therefore the default range will likely be -10 V to +10 V with an invalid oversampling rate. It is advised to set up these pins before acquiring ADC samples. |

Current Loops (4-20 mA measurement)

All 16 ADC channels independently support 4-20 mA current loop measurements. This is achieved by setting a pin jumper for the respective channel on the current loop enable pin header. Setting a jumper will electrically enable a 220 Ω 0.5% resistor from the ADC channel to ground allowing for a constant current measurement.

Thermistor

The TS-8820 supports up to 8 thermistors on channels 1 though 8. Support for a thermistor is enabled via software, the ADC pullup bit of TS-8820 FPGA register 0x2. Setting bit 8 enables a pull up on ADC channels 1 and 2, setting bit 9 enables a pull up on ADC channels 3 and 4, and setting bit 10 enables a pull up on channels 5 through 8. When enabled, each channel will get a separate 6.04 kΩ resistor to +12.5 V allowing the use of a thermistor probe.

ADC Usage

The 'ts8820ctl' application can be used to quickly sample the ADCs. This will send simultaneous sampling commands to each of the two ADC devices which will then sample all 16 channels in total the amount of times specified. See the "ts8820ctl.c" and "ts8820.c" files for examples on how this operation takes place.

For example, to sample all of the channels 5 times, the following command would be used:

ts8820ctl --sample=5

Collected 80 samples total.

Ch 1 Ch 2 Ch 3 Ch 4 Ch 5 Ch 6 Ch 7 Ch 8 Ch 9 Ch10 Ch11 Ch12 Ch13 Ch14 Ch15 Ch16

---- ---- ---- ---- ---- ---- ---- ---- ---- ---- ---- ---- ---- ---- ---- ----

-7626 2195 2193 2199 2192 2195 2195 2192 2189 2189 2193 2190 2189 2192 2191 2191

-7626 2194 2192 2198 2191 2194 2194 2191 2188 2189 2192 2189 2188 2191 2189 2190

-7626 2193 2191 2197 2190 2193 2193 2190 2187 2188 2191 2188 2186 2190 2189 2189

-7626 2189 2188 2193 2186 2189 2190 2186 2183 2184 2187 2184 2183 2186 2185 2185

-7626 2189 2187 2192 2186 2188 2189 2186 2183 2183 2187 2184 2182 2185 2184 2185

Above, channel 1 has a -7.62 V voltage source attached to it, all other channels are left unconnected. The range is set at -10 V to +10 V, and the oversampling rate is set to 64.

DAC Channels

The TS-8820 has 4 channels of 0 to +10 V DAC outputs. Each DAC channel has a positive and negative terminal connection. The negative side of the terminals are connected to the common ground of the TS-8820 and are non-isolated. The DAC terminals are on the P3 and P9 terminal blocks.

The DAC channels each have 12 bits of resolution that correspond to 0 to +10 V output. The upper bit (bit 15) of each register is a control bit that is used to synchronize the output of all 4 DAC channels. This means that all four registers can be updated without modifying the actual DAC output. Setting the control bit of any DAC channel register will case an update of the DAC output of all four channels. If the DAC register has not been modified, the update will still be sent but the actual output will remain the same. Reading this control bit will indicate if the synchronization is complete. Writing the DAC registers while the control bit is still asserted, indicating busy, will result in undefined behavior. The update process from setting the control bit to its completion takes approximately 3 microseconds.

When 0 is written to the control bit, the DAC values are updated internally in the FPGA but not transferred to the DAC. Thus any set of channels can be updated simultaneously by only writing a one on the final write.

The DAC channels can be controlled through 'ts8820ctl'. Note that the "--setdac" option to 'ts8820ctl' will always set the control bit of the selected register. See "ts8820ctl.c" and "ts8820.c" for an example of how this process works.

The following command would set DAC output 1 to 0.5 V:

ts8820ctl --setdac=1 --mvolts=500

H-Bridges

The TS-8820 supports 2 H-bridges on terminal block P6. One bridge drives terminals 1 and 2, and the second drives terminals 3 and 4. Each pair of terminals can be connected directly to a DC motor. Each H-bridge can supply up to 2.8A of current. See the PWM section for more information on how the H-bridges are driven.

Isolated CAN Port

The TS-8820 provides an isolated CAN port on the P10 terminal block. The CAN interface itself is from the SoM with the TS-8820 facilitating the isolated physical interface.

Optionally, a 124 ohm termination resistor can be electrically added by setting the Term. CAN jumper. The SocketCAN device is started by loading the driver thus:

modprobe sja1000_isa mem=0x81004c00 irq=65 clk=24000000

The CAN controller contained in the FPGA is compatible with the register interface for the SJA1000. This is implemented using SocketCAN.

Before proceeding with the examples, see the Kernel's CAN documentation here.

This board comes preinstalled with can-utils which can be used to communicate over a CAN network without writing any code. The candump utility can be used to dump all data on the network

## First, set the baud rate and bring up the device:

ip link set can0 type can bitrate 250000

ip link set can0 up

## Dump data & errors:

candump -cae can0,0:0,#FFFFFFFF &

## Send the packet with:

#can_id = 0x7df

#data 0 = 0x3

#data 1 = 0x1

#data 2 = 0x0c

cansend can0 7Df#03010c

This example packet is designed to work with the Ozen Elektronik myOByDic 1610 ECU simulator to read the RPM speed. This device will return data from candump with:

can0 7DF [3] 03 01 0C '...' can0 7E8 [8] 04 41 0C 2F C0 00 00 00 '.A./....' can0 7E9 [8] 04 41 0C 2F 80 00 00 00 '.A./....'

In this case, 0x2f is the current RPM value. This shows a simple way you can prove out the communication before moving to another language, but this next example sends the same packet and parses the same response in C:

#include <stdio.h>

#include <pthread.h>

#include <net/if.h>

#include <string.h>

#include <unistd.h>

#include <net/if.h>

#include <sys/ioctl.h>

#include <assert.h>

#include <linux/can.h>

#include <linux/can/raw.h>

int main(void)

{

int s;

int nbytes;

struct sockaddr_can addr;

struct can_frame frame;

struct ifreq ifr;

struct iovec iov;

struct msghdr msg;

char ctrlmsg[CMSG_SPACE(sizeof(struct timeval)) + CMSG_SPACE(sizeof(__u32))];

char *ifname = "can0";

if((s = socket(PF_CAN, SOCK_RAW, CAN_RAW)) < 0) {

perror("Error while opening socket");

return -1;

}

strcpy(ifr.ifr_name, ifname);

ioctl(s, SIOCGIFINDEX, &ifr);

addr.can_family = AF_CAN;

addr.can_ifindex = ifr.ifr_ifindex;

if(bind(s, (struct sockaddr *)&addr, sizeof(addr)) < 0) {

perror("socket");

return -2;

}

/* For the ozen myOByDic 1610 this requests the RPM guage */

frame.can_id = 0x7df;

frame.can_dlc = 3;

frame.data[0] = 3;

frame.data[1] = 1;

frame.data[2] = 0x0c;

nbytes = write(s, &frame, sizeof(struct can_frame));

if(nbytes < 0) {

perror("write");

return -3;

}

iov.iov_base = &frame;

msg.msg_name = &addr;

msg.msg_iov = &iov;

msg.msg_iovlen = 1;

msg.msg_control = &ctrlmsg;

iov.iov_len = sizeof(frame);

msg.msg_namelen = sizeof(struct sockaddr_can);

msg.msg_controllen = sizeof(ctrlmsg);

msg.msg_flags = 0;

do {

nbytes = recvmsg(s, &msg, 0);

if (nbytes < 0) {

perror("read");

return -4;

}

if (nbytes < (int)sizeof(struct can_frame)) {

fprintf(stderr, "read: incomplete CAN frame\n");

}

} while(nbytes == 0);

if(frame.data[0] == 0x4)

printf("RPM at %d of 255\n", frame.data[3]);

return 0;

}

Other languages have bindings to access CAN such as Python using C-types, Java using JNI.

Isolated RS-232

An isolated RS-232 port is on P10, with TX on terminal 7 and RX on terminal 8. The RS-232 port is driven by XUART1.

Isolated RS-485

An isolated RS-485 port is on P10. Terminals 5 and 6 are the + and - lines, respectively. The RS-485 port is driven by XUART0.

Relays

The TS-8820-4720 has four relays available at terminal block P8. All relays follow the same pattern Normally Open (NO), Common (COM), Normally Closed (NC). Relay 1 is pins 1-3, 2 is 4-6, 3 is 7-9, and 4 is 10-12. These relays are controlled via FPGA DIO on the TS-4720 computer module. For operational details please see the source code below.

// ts8820relays.c

// c. Technologic Systems, Inc. 2017

// Written by Michael D Peters.

// Cycles each relay on the TS-8820-47xx once per quarter second in an infinite loop.

// Assumes ts-8820-47xx. Toggles relays.

#include <stdio.h>

#include <sys/mman.h>

#include <fcntl.h>

#include <stdint.h>

int main(int argc, char* argv[])

{

int i, fb, mem = 0;

uint16_t *syscon = 0;

static int rotation[4] = {0x100, 0x80, 0x40, 0x10};

mem=open("/dev/mem", O_RDWR|O_SYNC);

syscon = mmap(0, getpagesize(), PROT_READ|PROT_WRITE, MAP_SHARED, mem, 0x80004000);

// Setup muxbus and turn on baseboard clock. No harm if it's already done, just a wasted cpu cycle.

syscon[0x4/2] = 0xF3FF; // TS-8820 needs as much delay as possible in muxbus configuration.

i = syscon[0x34/2];

syscon[0x34/2] = i | 0x1; // Bit 1 of 0x34 turns on baseboard clock. We don't want to disturb the other bits in that register.

syscon[0x18/2] = 0x1d0;

for(;;){

for(i = 0; i < 4; i++){

syscon[0x10/2] = rotation[i];

usleep(250000); // quarter second.

}

}

return 0;

}

Power Supply

The TS-8820 can be powered via PoE or direct DC voltage input to the terminal block connectors. If PoE is not used, power must be supplied on terminal block P6.

DC via Terminal Blocks

Direct power input can be applied to the P6 terminal block. There are three terminals for power and three for a ground connection. Each of the three sets of terminals are electrically connected together internally in the TS-8820. Operational range of the TS-8820 is +10 VDC to +30 VDC on these inputs. Supply an external ground on terminal 10, 11, and/or 12. Supply +10 V to +30 V on terminal 7, 8, and/or 9.

802.3af PoE

The TS-8820 is IEEE 802.3af PoE compliant. This allows the whole unit to be powered directly from a PoE sourcing device.

When powered via PoE, +24 VDC is made available on the P6 terminal block power terminals. Ensure that the total power draw of the system does not exceed the limits defined by IEEE 802.3af and that power is not also supplied to the TS-8820 on these pins!

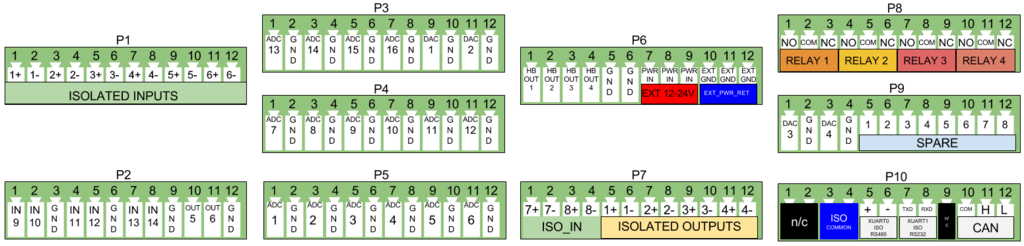

LEDS

The TS-8820 has 27 LEDs used to indicate the electrical status of the inputs and outputs on the device. LEDs are labelled as "LED#" on the PCB silkscreen.

The majority of the LEDs are not able to be directly controlled, they turn on or off as a reaction to the status of the I/O they are connected to. For example, when DIG_OUT1 is set, LED17 will turn on. The "System" LEDs are the exception to this and are controlled via the SoM LED interface.

| LED | FUNCTION | --- | LED | FUNCTION |

|---|---|---|---|---|

| 1 | System RED_LED | 2 | Doesn't exist. | |

| 3 | System Power | 4 | System GREEN_LED | |

| 5 | RELAY_1 | 6 | RELAY_2 | |

| 7 | RELAY_3 | 8 | RELAY_4 | |

| 9 | DIG_IN1 | 10 | DIG_IN2 | |

| 11 | DIG_IN3 | 12 | DIG_IN4 | |

| 13 | DIG_IN5 | 14 | DIG_IN6 | |

| 15 | DIG_IN7 | 16 | DIG_IN8 | |

| 17 | DIG_OUT1 | 18 | DIG_OUT2 | |

| 19 | DIG_OUT3 | 20 | DIG_OUT4 | |

| 21 | DIG_IN9 | 22 | DIG_IN10 | |

| 23 | DIG_IN11 | 24 | DIG_IN12 | |

| 25 | DIG_IN13 | 26 | DIG_IN14 | |

| 27 | DIG_OUT5 | 28 | DIG_OUT6 |

SPI

The GPIO on HD1 can optionally be used instead for SPI functionality through the SPI core on the TS-8820's FPGA. The TS-8820 uses the same FPGA-based SPI implementation as many other TS-SOCKET and SBCs. The simplest way to turn on the SPI controller is to set the HD1 override register to 0xFF00 thus:

devmem 0x8000800a 16 0xff00

The SPI controller exists at address offset 0xC0.

The table below is the register map for the SPI in the FPGA:

| Offset | Access | Bit(s) | Description |

|---|---|---|---|

| 0xC0 | Read Only | 15 | SPI MISO state |

| Read/Write | 14 | SPI CLK state | |

| Read/Write | 13:10 | Speed - 0 (highest), 1 (1/2 speed), 2 (1/4 speed)... | |

| Read/Write | 9:8 | LUN (0-3 representing the 4 chip selects) | |

| Read/Write | 7 | CS (1 - CS# is asserted) | |

| N/A | 6:1 | Reserved | |

| Read/Write | 0 | Speed | |

| 0xC2 | Read Only | 15:0 | Previous SPI read data from last write |

| 0xC4 | N/A | 15:0 | Reserved |

| 0xC6 | N/A | 15:0 | Reserved |

| 0xC8 | Read/Write | 15:0 | SPI read/write with CS# to stay asserted |

| 0xCa | Read Only | 15:0 | SPI pipelined read with CS# to stay asserted |

| 0xCc | Read/Write | 15:0 | SPI Read/Write with CS# to deassert post-op |

| 0xCe | N/A | 15:0 | Reserved |

The SPI clk state register should be set when CS# is deasserted. Value 0 makes SPI rising edge (CPOL=0), 1 is falling edge (CPOL=1). This only applies to speed >= 1. For speed == 0, SPI clock polarity/skew must be set from the PLL phase adjust registers in the syscon block.

Where the base clock is 75Mhz (extended temp alters this to 50Mhz), speed settings break down as follows:

0 - 75Mhz (/1) 1 - 37.5Mhz (/2) 2 - 18.75Mhz (/4) 3 - 12.5Mhz (/6) 4 - 9.375Mhz (/8) 5 - 7.5Mhz (/10) 6 - 6.25Mhz (/12) 7 - 5.36Mhz (/14) 8 - 4.68Mhz (/16) 9 - 4.17Mhz (/18) ... 15 - 2.5Mhz (/30) ... 19 - 1.97MHz (/38) ... 31 - 1.21MHz (/62)

The pipelined read register is for read bursts and will automatically start a subsequent SPI read upon completion of the requested SPI read. Reading from this register infers that another read will shortly follow and allows this SPI controller "a head start" on the next read for optimum read performance. This register should be accessed as long as there will be at least one more SPI read with CS# asserted to take place.

External Interfaces

Terminal Blocks

|

|

|

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

Ethernet Connector

The TS-8820 has a single 10/100 Ethernet port that can connect to any Ethernet LAN. The Ethernet connector includes LEDs indicating link and activity. The link LED should be on whenever the TS-8820 is powered and connected to a LAN. This connector allows the TS-8820 to be powered by PoE.

USB Host

The USB is available on two ports as a USB 2.0 host.

|

Button

There is a pushbutton between the two USB ports connected to the TS-4720 DIO_9 signal (read via TS-4720#syscon). This button is a simple GPIO button with no default behavior. One suggested usage is to use the button in the downstream application to signal a software induced reset or reboot.

DB9 Connector

|

|

HD1

TS-8820 Register Map

This register map assumes a base address offset. The offset when using the TS-4720 is 0x80008000. This address must first be activated using the MUXBUS enable and timing registers on the CPU module. On the TS-4720, write 0xF3FF to the address 0x80004004. Sample code for accessing the functions described in this table are largely encompassed by the ts8820ctl software available on the TS FTP Site.

| Offset | Bits | Description |

|---|---|---|

| 0x0 | 15:0 | Model ID: Reads 0x8820 |

| 0x2 | 15:11 | Reserved |

| 10 | Pull-up 5-8 enable | |

| 9 | Pull-up 3-4 enable | |

| 8 | Pull-up 1-2 enable | |

| 7 | H-bridge 2 enable (contacts go high-Z otherwise) | |

| 6 | H-bridge 1 enable (contacts go high-Z otherwise) | |

| 5 | H-bridge 2 direction | |

| 4 | H-bridge 1 direction | |

| 3:0 | FPGA Revision | |

| 0x4 | 15:14 | Reserved |

| 13:0 | Digital inputs 14:1 | |

| 0x6 | 15:10 | Reserved |

| 9:0 | SRAM Page register | |

| 0x8 | 15:12 | Reserved |

| 11:6 | Override Digital Outputs 6:1 with PWM | |

| 5:0 | Digital Output Values 6:1 | |

| 0xa | 7:0 | HD1 input values |

| 15:8 | SPI core override for HD1. 1 = SPI mode | |

| 0xc | 7:0 | HD1 output values (see HD1). |

| 15:8 | HD1 direction 1=drive output value 0=float pin | |

| 0xe | 15:0 | Reserved |

| 0x10 | 15:13 | PWM #1 Prescaler |

| 12:0 | PWM #1 Duty Cycle | |

| 0x12 | 15:13 | PWM #2 Prescalar |

| 12:0 | PWM #2 Duty Cycle | |

| 0x14 | 15:13 | PWM #3 Prescaler |

| 12:0 | PWM #3 Duty Cycle | |

| 0x16 | 15:13 | PWM #4 Prescaler |

| 12:0 | PWM #4 Duty Cycle | |

| 0x18 | 15:13 | PWM #5 Prescaler |

| 12:0 | PWM #5 Duty Cycle | |

| 0x1a | 15:13 | PWM #6 Prescaler |

| 12:0 | PWM #6 Duty Cycle | |

| 0x1c | 15:13 | PWM #7 Prescaler |

| 12:0 | PWM #7 Duty Cycle | |

| 0x1e | 15:13 | PWM #8 Prescaler |

| 12:0 | PWM #8 Duty Cycle | |

| 0x20 | 15:0 | Pulse Counter #1 (RO) |

| 0x22 | 15:0 | Pulse Counter #2 (RO) |

| 0x24 | 15:0 | Pulse Counter #3 (RO) |

| 0x26 | 15:0 | Pulse Counter #4 (RO) |

| 0x28 | 15:0 | Pulse Counter #5 (RO) |

| 0x2a | 15:0 | Pulse Counter #6 (RO) |

| 0x2c | 15:0 | Pulse Counter #7 (RO) |

| 0x2e | 15:0 | Pulse Counter #8 (RO) |

| 0x30 | 15:0 | Pulse Counter #9 (RO) |

| 0x32 | 15:0 | Pulse Counter #10 (RO) |

| 0x34 | 15:0 | Pulse Counter #11 (RO) |

| 0x36 | 15:0 | Pulse Counter #12 (RO) |

| 0x38 | 15:0 | Pulse Counter #13 (RO) |

| 0x3a | 15:0 | Pulse Counter #14 (RO) |

| 0x3c | 15:0 | Reserved |

| 0x3e | 15:0 | Reserved |

| 0x80 | 15:0 | ADC Core ID (reads 0xadc1) |

| 0x82 | 15:8 | ADC Channel Mask (0 = do not save channel data) |

| 7:6 | Highest number chip to use (0-3, if 01 then sample chip 0 and chip 1) | |

| 5 | 1 = Force standby | |

| 4 | 1 = Use standby between samples to save power | |

| 3 | 1 = Smart DMA IRQ mode | |

| 2 | 1 = Enable IRQ | |

| 1 | 1 = Collect samples, 0 = stop | |

| 0 | 1 = Reset ADC chips and all FIFOs | |

| 0x84 | 15 | 1 = There has been a FIFO overflow since last reset |

| 14:0 | Number of samples available to be read | |

| 0x86 | 15:0 | Sample Data (RO) |

| 0x88 | 15:0 | Sampling period LSB (RW) |

| 0x8a | 15:0 | Sampling period MSB (RW) |

| 0x8c | 15:0 | IRQ Threshold (RW) |

| 0x8e | 15:0 | Reserved |

| 0x90 | 15:0 | Reserved |

| 0x92 | 15:0 | Reserved |

| 0x94 | 15:0 | Reserved |

| 0x96 | 15:0 | Reserved |

| 0x98 | 15:0 | Reserved |

| 0x9a | 15:0 | Reserved |

| 0x9c | 15:0 | Reserved |

| 0x9e | 15:0 | Reserved |

| 0xa0 | 15:0 | DAC 1 Control Register |

| 0xa2 | 15:0 | DAC 2 Control Register |

| 0xa4 | 15:0 | DAC 3 Control Register |

| 0xa6 | 15:0 | DAC 4 Control Register |

Product Notes

FCC Advisory

This equipment generates, uses, and can radiate radio frequency energy and if not installed and used properly (that is, in strict accordance with the manufacturer's instructions), may cause interference to radio and television reception. It has been type tested and found to comply with the limits for a Class A digital device in accordance with the specifications in Part 15 of FCC Rules, which are designed to provide reasonable protection against such interference when operated in a commercial environment. Operation of this equipment in a residential area is likely to cause interference, in which case the owner will be required to correct the interference at his own expense.

If this equipment does cause interference, which can be determined by turning the unit on and off, the user is encouraged to try the following measures to correct the interference:

Reorient the receiving antenna. Relocate the unit with respect to the receiver. Plug the unit into a different outlet so that the unit and receiver are on different branch circuits. Ensure that mounting screws and connector attachment screws are tightly secured. Ensure that good quality, shielded, and grounded cables are used for all data communications. If necessary, the user should consult the dealer or an experienced radio/television technician for additional suggestions. The following booklets prepared by the Federal Communications Commission (FCC) may also prove helpful:

How to Identify and Resolve Radio-TV Interference Problems (Stock No. 004-000-000345-4) Interface Handbook (Stock No. 004-000-004505-7) These booklets may be purchased from the Superintendent of Documents, U.S. Government Printing Office, Washington, DC 20402.

Limited Warranty

See our Terms and Conditions for more details.