TS-POE100: Difference between revisions

| Line 160: | Line 160: | ||

# of it | # of it | ||

ifconfig eth1 down # assuming eth1 is the TS-POE100 on your board | ifconfig eth1 down # assuming eth1 is the TS-POE100 on your board | ||

#This example uses the [[TS-7800]]'s registers | #This example uses the [[TS-7800]]'s registers | ||

#Use [[peekpoke]] to change the ASIX MAC registers: | #Use [[peekpoke]] to change the ASIX MAC registers: | ||

Revision as of 17:20, 27 May 2011

| |

| Documents | |

|---|---|

| Schematic | |

| ASIX Documentation |

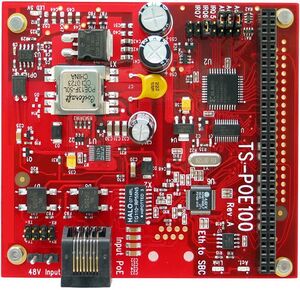

Overview

The TS-POE100 is a PC/104 peripheral board (standard format) that provides a 10/100 Ethernet port integrated with a Power-over-Ethernet splitter circuit, which is capable to provide up to 12W of power through the PC/104 bus.

The TS-POE100 features a Linear Technology LTC4267 PoE chip fully compatible with the IEEE 802.3af specification. The TS-POE100 is a Power-over-Ethernet splitter interface that provides up to 12W (2.4A @ 5V) to external devices (class 3 devices). The internal switching-regulator delivers regulated 5VDC to the PC/104 connector, enabling a complete stackable SBC system to be powered.

In addition, the TS-POE100 provides an integrated 10/100 ethernet port through the ASIX AX88796B embedded MAC with on-chip PHY. It interfaces with the PC/104 connector via 16-bit data bus and the register map is NE2000 compatible. The ASIX solution features Wake-on-LAN functionality, enabling the Ethernet chip to enter in sleep mode with programmed wake-up on the reception of a magic network package. Once integrated with the PoE, this function allows a complete SBC system to enter power-save mode and to wake-up through the network whenever wanted.

Hardware Configuration

The TS-POE100 jumpers select one-of-three IRQ lines and one-of-four I/O address regions. Also, it is possible to do PC/104 16-bit access using only the 64-pin PC/104 connector in ARM mode if the ARM jumper is ON. Jumpers IRQ5, IRQ6 and IRQ7 selects the desired ISA IRQ line for the TS-POE100 MAC.

I/O Address

The PLD and MAC I/O address locations can be configured using jumpers Add1 and Add2 according to the table below:

| PLD I/O | MAC I/O | Add1 | Add2 |

|---|---|---|---|

| 0x100 | 0x200 | Off | Off |

| 0x110 | 0x240 | On | Off |

| 0x120 | 0x300 | Off | On |

| 0x130 | 0x340 | On | On |

Base Register Map

The TS-POE100 has 4 registers of 4-bits each which appear implemented on the PLD.

| I/O Addr | Description | Data Access | Bits |

|---|---|---|---|

| Base+0x0 | Board identifier | Read Only | returns 0x5 unique ID to verify presence |

| Base+0x4 | PLD revision | Read Only | Returns PLD revision |

| Base+0x8 | SRAM Control Register | Read Only | bit 3 = IRQ7 jumper status (1=ON, 0=OFF)

bit 2 = IRQ6 jumper status (1=ON, 0=OFF) bit 1 = IRQ5 jumper status (1=ON, 0=OFF) bit 0 = ARM jumper status (1=ON, 0=OFF) |

| Base+0xC | PC104 Power Control | Bit 0 is RW | bit 3:1 = reserved

bit 0 = 5VDC power to PC/104 bus control (0=power ON, 1=power OFF) |

For a complete description of the MAC register map (which is NE2000 compatible), please refer to the ASIX AX88796B documentation.

Power Input and Assembly

In order to power up a system including a PC/104 computer and a TS-POE100, the only required cable/connection is the POE ethernet cable, which must include network signals and power. Connect it to the TS-POE100 RJ45 connector.

Power can be either on the spare pairs or on the data pairs of the 8-lines network cable. The power level that should be found at the network cable is 48VDC @ 0.35A. If the TS-POE100 detects valid POE signature and classification stages, it will transmit regulated 5VDC to the PC/104 bus, powering up the other boards (peripherals and computers) connected to it. The on-board green LED named LED 5V will come on in case the TS-POE100 detects a valid POE power source. Also, there are on-board LEDs for the MAC - Link and Network Activity.

The TS-POE100 can provide up to 12W of power (2.4Amp @ 5VDC) – this is Class 3 POE implementation.

Software Support

Loading the Module

The register map of ASIX AX88796B ethernet chip is NE2000 compatible, so driver support is straight-forward.

You can load the module like this:

. /initrd/ts7800.subr # to load the pc104on function

pc104on # to enable pc104

modprobe ax88796b mem=0x200 irq=6 # Replace the irq option with your IRQ jumper configuration

If If you receive a message that the ax88796b module cannot be found then you will need to compile the module for your kernel.

Wake on lan

The Asix chip enables the POE board to toggle power to the PC104 bus with a magic frame. In order to this, the ASIX chip on the TS-POE100 must be set into this mode on shutdown.

First, bring down the interface:

# you cannot change the page window

# until the driver releases control

# of it

ifconfig eth1 down # assuming eth1 is the TS-POE100 on your board

#This example uses the [[TS-7800]]'s registers

#Use [[peekpoke]] to change the ASIX MAC registers:

# Sets the page window to 3 where the

peekpoke 8 0xEF000200 0xe2

# Wakeup Control and Status Register (WUCSR) (Offset 0a)

# this value tells the ASIX to enable the wakeup frame

peekpoke 8 0xEF00020A 1

# Power Management Register (PMR) (Offset 0b)

# Sets the board to D1 status where it stops listening

# for normal data and only listens for the magic wake up frame

peekpoke 8 0xEF00020B 1

# Sync to save your disk changes

sync

# the sd card driver can technically take .1 seconds to complete

# a write, so just to be safe

sleep 1

# This tells the TS-POE100 to stop supplying power down the PC104 bridge

# This kills the CPU

peekpoke 8 0xEE00010C 1