TS-POE100: Difference between revisions

No edit summary |

|||

| (10 intermediate revisions by 3 users not shown) | |||

| Line 2: | Line 2: | ||

|title = TS-POE100 | |title = TS-POE100 | ||

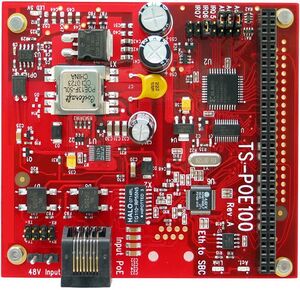

|image = [[File:Ts-poe100.jpg|300px]] | |image = [[File:Ts-poe100.jpg|300px]] | ||

|titlestyle | |titlestyle = | ||

|headerstyle = background:#ccf; | |headerstyle = background:#ccf; | ||

|labelstyle | |labelstyle = width:33% | ||

|datastyle | |datastyle = | ||

|header1 = Documents | |header1 = Documents | ||

|data2 = [ | |data2 = [https://cdn.embeddedTS.com/resource-attachments/ts-poe100-schematic.pdf Schematic] | ||

|data3 = [http://www.asix.com.tw/products.php?op=pItemdetail&PItemID=80;65;86 ASIX Documentation] | |data3 = [http://www.asix.com.tw/products.php?op=pItemdetail&PItemID=80;65;86 ASIX Documentation] | ||

}} | }} | ||

= Overview = | |||

The TS-POE100 is a PC/104 peripheral board (standard format) that provides a 10/100 | The TS-POE100 is a PC/104 peripheral board (standard format) that provides a 10/100 Ethernet port integrated with a Power-over-Ethernet splitter circuit, which is capable to provide up to 12W of power through the PC/104 bus. | ||

Ethernet port integrated with a Power-over-Ethernet splitter circuit, which is capable to | |||

provide up to 12W of power through the PC/104 bus | |||

The TS-POE100 features a Linear Technology LTC4267 PoE chip fully compatible with the IEEE 802.3af specification. The TS-POE100 is a Power-over-Ethernet splitter interface that | |||

provides up to 12W (2.4A @ 5V) to external devices (class 3 devices). The internal switching-regulator delivers regulated 5VDC to the PC/104 connector, enabling a complete stackable SBC system to be powered. | |||

the | |||

In addition, the TS-POE100 provides an integrated 10/100 ethernet port through the ASIX AX88796B embedded MAC with on-chip PHY. It interfaces with the PC/104 connector via 16-bit data bus and the register map is NE2000 compatible. | |||

The TS-POE100 jumpers select one-of-three IRQ lines and one-of-four I/O address regions. | = Hardware Configuration = | ||

Also, it is possible to do PC/104 16-bit access using only the 64-pin PC/104 connector in | The TS-POE100 jumpers select one-of-three IRQ lines and one-of-four I/O address regions. Also, it is possible to do PC/104 16-bit access using only the 64-pin PC/104 connector in ARM mode if the ARM jumper is ON. Jumpers IRQ5, IRQ6 and IRQ7 selects the desired ISA IRQ line for the TS-POE100 MAC. | ||

ARM mode if the ARM jumper is ON. Jumpers IRQ5, IRQ6 and IRQ7 selects the desired ISA | |||

IRQ line for the TS-POE100 MAC. | |||

==I/O Address== | |||

The PLD and MAC I/O address locations can be configured using jumpers Add1 and Add2 | The PLD and MAC I/O address locations can be configured using jumpers Add1 and Add2 according to the table below: | ||

according to the table below: | |||

{| class="wikitable" | {| class="wikitable" | ||

| Line 70: | Line 53: | ||

|} | |} | ||

== Base Register Map == | |||

The TS-POE100 has 4 registers of 4-bits each which appear implemented on the PLD. | The TS-POE100 has 4 registers of 4-bits each which appear implemented on the PLD. | ||

| Line 114: | Line 96: | ||

|} | |} | ||

For a complete description of the MAC register map (which is NE2000 compatible), please | For a complete description of the MAC register map (which is NE2000 compatible), please refer to the ASIX AX88796B documentation. | ||

refer to the ASIX AX88796B documentation. | |||

==Power Input and Assembly== | |||

In order to power up a system including a PC/104 computer and a TS-POE100, the only required cable/connection is the POE ethernet cable, which must include network signals and power. Connect it to the TS-POE100 RJ45 connector. | |||

Power can be either on the spare pairs or on the data pairs of the 8-lines network cable. The power level that should be found at the network cable is 48VDC @ 0.35A. If the TS-POE100 detects valid POE signature and classification stages, it will transmit regulated 5VDC to the PC/104 bus, powering up the other boards (peripherals and computers) connected to it. The on-board green LED named LED 5V will come on in case the TS-POE100 detects a valid POE power source. Also, there are on-board LEDs for the MAC - Link and Network Activity. | |||

and | |||

The TS-POE100 can provide up to 12W of power (2.4Amp @ 5VDC) – this is Class 3 POE implementation. | |||

= Software Support = | |||

== Loading the Module == | |||

The register map of ASIX AX88796B ethernet chip is NE2000 compatible, so driver support is straight-forward. | |||

The register map of ASIX AX88796B ethernet chip is NE2000 compatible, so driver support | |||

is straight-forward. | |||

You can load the module like this: | You can load the module like this: | ||

<SyntaxHighlight lang=bash> | <SyntaxHighlight lang=bash> | ||

modprobe ax88796b mem=0x200 irq=6 # Replace the irq option with your IRQ jumper configuration | modprobe ax88796b mem=0x200 irq=6 # Replace the irq option with your IRQ jumper configuration | ||

</SyntaxHighlight> | </SyntaxHighlight> | ||

| Line 151: | Line 117: | ||

If If you receive a message that the ax88796b module cannot be found then you will need to compile the module for your kernel. | If If you receive a message that the ax88796b module cannot be found then you will need to compile the module for your kernel. | ||

You also may need to turn the pc104 adapter to pc104 mode as some boards default to a gpio state. | |||

<SyntaxHighlight lang=bash> | <SyntaxHighlight lang=bash> | ||

# | . /initrd/ts7800.subr # to load the pc104on function for the 7800 | ||

pc104on # to enable pc104 | |||

</SyntaxHighlight> | |||

# | |||

{{:General Footer}} | |||

== Usage with 3rd party devices == | |||

{{:Third Party PC/104}} | |||

Latest revision as of 12:46, 22 June 2023

| |

| Documents | |

|---|---|

| Schematic | |

| ASIX Documentation |

Overview

The TS-POE100 is a PC/104 peripheral board (standard format) that provides a 10/100 Ethernet port integrated with a Power-over-Ethernet splitter circuit, which is capable to provide up to 12W of power through the PC/104 bus.

The TS-POE100 features a Linear Technology LTC4267 PoE chip fully compatible with the IEEE 802.3af specification. The TS-POE100 is a Power-over-Ethernet splitter interface that provides up to 12W (2.4A @ 5V) to external devices (class 3 devices). The internal switching-regulator delivers regulated 5VDC to the PC/104 connector, enabling a complete stackable SBC system to be powered.

In addition, the TS-POE100 provides an integrated 10/100 ethernet port through the ASIX AX88796B embedded MAC with on-chip PHY. It interfaces with the PC/104 connector via 16-bit data bus and the register map is NE2000 compatible.

Hardware Configuration

The TS-POE100 jumpers select one-of-three IRQ lines and one-of-four I/O address regions. Also, it is possible to do PC/104 16-bit access using only the 64-pin PC/104 connector in ARM mode if the ARM jumper is ON. Jumpers IRQ5, IRQ6 and IRQ7 selects the desired ISA IRQ line for the TS-POE100 MAC.

I/O Address

The PLD and MAC I/O address locations can be configured using jumpers Add1 and Add2 according to the table below:

| PLD I/O | MAC I/O | Add1 | Add2 |

|---|---|---|---|

| 0x100 | 0x200 | Off | Off |

| 0x110 | 0x240 | On | Off |

| 0x120 | 0x300 | Off | On |

| 0x130 | 0x340 | On | On |

Base Register Map

The TS-POE100 has 4 registers of 4-bits each which appear implemented on the PLD.

| I/O Addr | Description | Data Access | Bits |

|---|---|---|---|

| Base+0x0 | Board identifier | Read Only | returns 0x5 unique ID to verify presence |

| Base+0x4 | PLD revision | Read Only | Returns PLD revision |

| Base+0x8 | SRAM Control Register | Read Only | bit 3 = IRQ7 jumper status (1=ON, 0=OFF)

bit 2 = IRQ6 jumper status (1=ON, 0=OFF) bit 1 = IRQ5 jumper status (1=ON, 0=OFF) bit 0 = ARM jumper status (1=ON, 0=OFF) |

| Base+0xC | PC104 Power Control | Bit 0 is RW | bit 3:1 = reserved

bit 0 = 5VDC power to PC/104 bus control (0=power ON, 1=power OFF) |

For a complete description of the MAC register map (which is NE2000 compatible), please refer to the ASIX AX88796B documentation.

Power Input and Assembly

In order to power up a system including a PC/104 computer and a TS-POE100, the only required cable/connection is the POE ethernet cable, which must include network signals and power. Connect it to the TS-POE100 RJ45 connector.

Power can be either on the spare pairs or on the data pairs of the 8-lines network cable. The power level that should be found at the network cable is 48VDC @ 0.35A. If the TS-POE100 detects valid POE signature and classification stages, it will transmit regulated 5VDC to the PC/104 bus, powering up the other boards (peripherals and computers) connected to it. The on-board green LED named LED 5V will come on in case the TS-POE100 detects a valid POE power source. Also, there are on-board LEDs for the MAC - Link and Network Activity.

The TS-POE100 can provide up to 12W of power (2.4Amp @ 5VDC) – this is Class 3 POE implementation.

Software Support

Loading the Module

The register map of ASIX AX88796B ethernet chip is NE2000 compatible, so driver support is straight-forward.

You can load the module like this:

modprobe ax88796b mem=0x200 irq=6 # Replace the irq option with your IRQ jumper configuration

If If you receive a message that the ax88796b module cannot be found then you will need to compile the module for your kernel.

You also may need to turn the pc104 adapter to pc104 mode as some boards default to a gpio state.

. /initrd/ts7800.subr # to load the pc104on function for the 7800

pc104on # to enable pc104

Product Notes

FCC Advisory

This equipment generates, uses, and can radiate radio frequency energy and if not installed and used properly (that is, in strict accordance with the manufacturer's instructions), may cause interference to radio and television reception. It has been type tested and found to comply with the limits for a Class A digital device in accordance with the specifications in Part 15 of FCC Rules, which are designed to provide reasonable protection against such interference when operated in a commercial environment. Operation of this equipment in a residential area is likely to cause interference, in which case the owner will be required to correct the interference at his own expense.

If this equipment does cause interference, which can be determined by turning the unit on and off, the user is encouraged to try the following measures to correct the interference:

Reorient the receiving antenna. Relocate the unit with respect to the receiver. Plug the unit into a different outlet so that the unit and receiver are on different branch circuits. Ensure that mounting screws and connector attachment screws are tightly secured. Ensure that good quality, shielded, and grounded cables are used for all data communications. If necessary, the user should consult the dealer or an experienced radio/television technician for additional suggestions. The following booklets prepared by the Federal Communications Commission (FCC) may also prove helpful:

How to Identify and Resolve Radio-TV Interference Problems (Stock No. 004-000-000345-4) Interface Handbook (Stock No. 004-000-004505-7) These booklets may be purchased from the Superintendent of Documents, U.S. Government Printing Office, Washington, DC 20402.

Limited Warranty

See our Terms and Conditions for more details.

Usage with 3rd party devices

Please note that while efforts are made to follow the PC/104 specification this peripheral is not tested with third party SBCs or connected peripherals. This card is not guaranteed to operate as intended when third party PC104 peripherals or SBCs are connected.