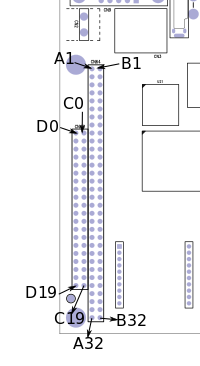

TS-7250-V3 PC104 Header

From embeddedTS Manuals

The PC/104 connector consists of four rows of pins labelled A-D. This header implements the #PC104 Bus, and optionally most pins can be GPIO.

Refer to the IO specifications for details on the IO voltages of these pins. Not all pins on the PC/104 bus are designed to be 5V tolerant, but will be in places where it is needed for compatibility with the bus.

| Pins | IO Specification |

|---|---|

| D3-D15 [1] | PCA9555 |

| A1 | CPU 3.3V |

| A10, A11, A12-A31, B6, B8, B11-B20, B25-B28, B30, D1-D2 | FPGA 3.3-V LVTTL |

| A2-A9, B4, B21-B23, C11-C18 | FPGA 3.3-V LVTTL+QS3861 |

| B2 | Open drain with pull to 5V |

- ↑ These are only present on the models with the optional I2C port expander

- ↑ Outputs a continuous 14.318180 MHz clock

- ↑ 2.0 2.1 2.2 Powering the system from PC104 5V prevents the Board's low power sleep mode from functioning.

- ↑ This pin can be used to supply power to the board through the switching regulator.

- ↑ This is automatically pulsed on startup by the ts-pc104 driver as ISA_RESET