TS-7250-V3 PC104 Header: Difference between revisions

From embeddedTS Manuals

No edit summary |

No edit summary |

||

| Line 46: | Line 46: | ||

| GND | | GND | ||

| A31 | | A31 | ||

| [[#PC104_Bus|ISA_ADD_00]]/[[#GPIO| | | [[#PC104_Bus|ISA_ADD_00]]/[[#GPIO|Chip 50004064.fpga_gpio IO 0]] | ||

|- | |- | ||

| B30 | | B30 | ||

| ISA_14_3_MHZ <ref>Outputs a continuous 14.318180 MHz clock</ref> | | ISA_14_3_MHZ <ref>Outputs a continuous 14.318180 MHz clock</ref> | ||

| A30 | | A30 | ||

| [[#PC104_Bus|ISA_ADD_01]]/[[#GPIO| | | [[#PC104_Bus|ISA_ADD_01]]/[[#GPIO|Chip 50004064.fpga_gpio IO 1]] | ||

|- | |- | ||

| B29 | | B29 | ||

| +5V <ref name=pc1045v>Powering the system from PC104 5V prevents the Board's low power sleep mode from functioning.</ref> | | +5V <ref name=pc1045v>Powering the system from PC104 5V prevents the Board's low power sleep mode from functioning.</ref> | ||

| A29 | | A29 | ||

| [[#PC104_Bus|ISA_ADD_02]]/[[#GPIO| | | [[#PC104_Bus|ISA_ADD_02]]/[[#GPIO|Chip 50004064.fpga_gpio IO 2]] | ||

|- | |- | ||

| B28 | | B28 | ||

| [[#GPIO| | | [[#GPIO|Chip 50004040.fpga_gpio IO 1]]/[[#PC104_Bus|TS mode DAT15]] | ||

| A28 | | A28 | ||

| [[#PC104_Bus|ISA_ADD_03]]/[[#GPIO| | | [[#PC104_Bus|ISA_ADD_03]]/[[#GPIO|Chip 50004064.fpga_gpio IO 3]] | ||

| C19 | | C19 | ||

| GND | | GND | ||

| Line 68: | Line 68: | ||

|- | |- | ||

| B27 | | B27 | ||

| [[#GPIO| | | [[#GPIO|Chip 50004040.fpga_gpio IO 2]]/[[#PC104_Bus|TS mode DAT14]] | ||

| A27 | | A27 | ||

| [[#PC104_Bus|ISA_ADD_04]]/[[#GPIO| | | [[#PC104_Bus|ISA_ADD_04]]/[[#GPIO|Chip 50004064.fpga_gpio IO 4]] | ||

| C18 | | C18 | ||

| [[#PC104_Bus|ISA_DAT_15]]/[[#GPIO| | | [[#PC104_Bus|ISA_DAT_15]]/[[#GPIO|Chip 5000405c.fpga_gpio IO 15]] | ||

| D18 | | D18 | ||

| GND | | GND | ||

|- | |- | ||

| B26 | | B26 | ||

| [[#GPIO| | | [[#GPIO|Chip 50004040.fpga_gpio IO 10]]/[[#PC104_Bus|TS mode DAT13]] | ||

| A26 | | A26 | ||

| [[#PC104_Bus|ISA_ADD_05]]/[[#GPIO| | | [[#PC104_Bus|ISA_ADD_05]]/[[#GPIO|Chip 50004064.fpga_gpio IO 5]] | ||

| C17 | | C17 | ||

| [[#PC104_Bus|ISA_DAT_14]]/[[#GPIO| | | [[#PC104_Bus|ISA_DAT_14]]/[[#GPIO|Chip 5000405c.fpga_gpio IO 14]] | ||

| D17 | | D17 | ||

| Unused | | Unused | ||

| Line 88: | Line 88: | ||

| [[#FPGA_IRQs|FPGA IRQ 13]]/[[#PC104_Bus|TS mode DAT11]] | | [[#FPGA_IRQs|FPGA IRQ 13]]/[[#PC104_Bus|TS mode DAT11]] | ||

| A25 | | A25 | ||

| [[#PC104_Bus|ISA_ADD_06]]/[[#GPIO| | | [[#PC104_Bus|ISA_ADD_06]]/[[#GPIO|Chip 50004064.fpga_gpio IO 6]] | ||

| C16 | | C16 | ||

| [[#PC104_Bus|ISA_DAT_13]]/[[#GPIO| | | [[#PC104_Bus|ISA_DAT_13]]/[[#GPIO|Chip 5000405c.fpga_gpio IO 13]] | ||

| D16 | | D16 | ||

| +5V <ref name=pc1045v /> | | +5V <ref name=pc1045v /> | ||

| Line 97: | Line 97: | ||

| GND | | GND | ||

| A24 | | A24 | ||

| [[#PC104_Bus|ISA_ADD_07]]/[[#GPIO| | | [[#PC104_Bus|ISA_ADD_07]]/[[#GPIO|Chip 50004064.fpga_gpio IO 7]] | ||

| C15 | | C15 | ||

| [[#PC104_Bus|ISA_DAT_12]]/[[#GPIO| | | [[#PC104_Bus|ISA_DAT_12]]/[[#GPIO|Chip 5000405c.fpga_gpio IO 12]] | ||

| D15 | | D15 | ||

| [[#GPIO| | | [[#GPIO|Chip 50004054.fpga_gpio IO 12]] | ||

|- | |- | ||

| B23 | | B23 | ||

| [[#FPGA_IRQs|FPGA IRQ 14]] | | [[#FPGA_IRQs|FPGA IRQ 14]] | ||

| A23 | | A23 | ||

| [[#PC104_Bus|ISA_ADD_08]]/[[#GPIO| | | [[#PC104_Bus|ISA_ADD_08]]/[[#GPIO|Chip 50004064.fpga_gpio IO 8]] | ||

| C14 | | C14 | ||

| [[#PC104_Bus|ISA_DAT_11]]/[[#GPIO| | | [[#PC104_Bus|ISA_DAT_11]]/[[#GPIO|Chip 5000405c.fpga_gpio IO 11]] | ||

| D14 | | D14 | ||

| [[#GPIO| | | [[#GPIO|Chip 50004054.fpga_gpio IO 11]] | ||

|- | |- | ||

| B22 | | B22 | ||

| [[#FPGA_IRQs|FPGA IRQ 15]] | | [[#FPGA_IRQs|FPGA IRQ 15]] | ||

| A22 | | A22 | ||

| [[#PC104_Bus|ISA_ADD_09]]/[[#GPIO| | | [[#PC104_Bus|ISA_ADD_09]]/[[#GPIO|Chip 50004064.fpga_gpio IO 9]] | ||

| C13 | | C13 | ||

| [[#PC104_Bus|ISA_DAT_10]]/[[#GPIO| | | [[#PC104_Bus|ISA_DAT_10]]/[[#GPIO|Chip 5000405c.fpga_gpio IO 10]] | ||

| D13 | | D13 | ||

| [[#GPIO| | | [[#GPIO|Chip 50004054.fpga_gpio IO 10]] | ||

|- | |- | ||

| B21 | | B21 | ||

| [[#FPGA_IRQs|FPGA IRQ 16]] | | [[#FPGA_IRQs|FPGA IRQ 16]] | ||

| A21 | | A21 | ||

| [[#PC104_Bus|ISA_ADD_10]]/[[#GPIO| | | [[#PC104_Bus|ISA_ADD_10]]/[[#GPIO|Chip 50004064.fpga_gpio IO 10]] | ||

| C12 | | C12 | ||

| [[#PC104_Bus|ISA_DAT_09]]/[[#GPIO| | | [[#PC104_Bus|ISA_DAT_09]]/[[#GPIO|Chip 5000405c.fpga_gpio IO 9]] | ||

| D12 | | D12 | ||

| [[#GPIO| | | [[#GPIO|Chip 50004054.fpga_gpio IO 9]] | ||

|- | |- | ||

| B20 | | B20 | ||

| [[#PC104_Bus|TS mode DAT12]] | | [[#PC104_Bus|TS mode DAT12]] | ||

| A20 | | A20 | ||

| [[#PC104_Bus|ISA_ADD_11]]/[[#GPIO| | | [[#PC104_Bus|ISA_ADD_11]]/[[#GPIO|Chip 50004064.fpga_gpio IO 11]] | ||

| C11 | | C11 | ||

| [[#PC104_Bus|ISA_DAT_08]]/[[#GPIO| | | [[#PC104_Bus|ISA_DAT_08]]/[[#GPIO|Chip 5000405c.fpga_gpio IO 8]] | ||

| D11 | | D11 | ||

| [[#GPIO| | | [[#GPIO|Chip 50004054.fpga_gpio IO 8]] | ||

|- | |- | ||

| B19 | | B19 | ||

| [[#GPIO| | | [[#GPIO|Chip 50004040.fpga_gpio IO 6]] | ||

| A19 | | A19 | ||

| [[#PC104_Bus|ISA_ADD_12]]/[[#GPIO| | | [[#PC104_Bus|ISA_ADD_12]]/[[#GPIO|Chip 50004064.fpga_gpio IO 12]] | ||

| C10 | | C10 | ||

| Unused | | Unused | ||

| D10 | | D10 | ||

| [[#GPIO| | | [[#GPIO|Chip 50004054.fpga_gpio IO 7]] | ||

|- | |- | ||

| B18 | | B18 | ||

| [[#GPIO| | | [[#GPIO|Chip 50004040.fpga_gpio IO 7]]/[[#PC104_Bus|TS mode DAT10]] | ||

| A18 | | A18 | ||

| [[#PC104_Bus|ISA_ADD_13]]/[[#GPIO| | | [[#PC104_Bus|ISA_ADD_13]]/[[#GPIO|Chip 50004064.fpga_gpio IO 13]] | ||

| C09 | | C09 | ||

| Unused | | Unused | ||

| D09 | | D09 | ||

| [[#GPIO| | | [[#GPIO|Chip 50004054.fpga_gpio IO 6]] | ||

|- | |- | ||

| B17 | | B17 | ||

| [[#GPIO| | | [[#GPIO|Chip 50004040.fpga_gpio IO 8]]/[[#PC104_Bus|TS mode DAT9]] | ||

| A17 | | A17 | ||

| [[#PC104_Bus|ISA_ADD_14]]/[[#GPIO| | | [[#PC104_Bus|ISA_ADD_14]]/[[#GPIO|Chip 50004064.fpga_gpio IO 14]] | ||

| C08 | | C08 | ||

| Unused | | Unused | ||

| D08 | | D08 | ||

| [[#GPIO| | | [[#GPIO|Chip 50004054.fpga_gpio IO 5]] | ||

|- | |- | ||

| B16 | | B16 | ||

| [[#GPIO| | | [[#GPIO|Chip 50004040.fpga_gpio IO 12]] | ||

| A16 | | A16 | ||

| [[#PC104_Bus|ISA_ADD_15]]/[[#GPIO| | | [[#PC104_Bus|ISA_ADD_15]]/[[#GPIO|Chip 50004064.fpga_gpio IO 15]] | ||

| C07 | | C07 | ||

| Unused | | Unused | ||

| D07 | | D07 | ||

| [[#GPIO| | | [[#GPIO|Chip 50004054.fpga_gpio IO 4]] | ||

|- | |- | ||

| B15 | | B15 | ||

| [[#GPIO| | | [[#GPIO|Chip 50004040.fpga_gpio IO 13]] | ||

| A15 | | A15 | ||

| [[#PC104_Bus|ISA_ADD_16]]/[[#GPIO| | | [[#PC104_Bus|ISA_ADD_16]]/[[#GPIO|Chip 5000406c.fpga_gpio IO 0]] | ||

| C06 | | C06 | ||

| Unused | | Unused | ||

| D06 | | D06 | ||

| [[#GPIO| | | [[#GPIO|Chip 50004054.fpga_gpio IO 3]] | ||

|- | |- | ||

| B14 | | B14 | ||

| [[#PC104_Bus|ISA_IOR]]/[[#GPIO| | | [[#PC104_Bus|ISA_IOR]]/[[#GPIO|Chip 5000406c.fpga_gpio IO 4]] | ||

| A14 | | A14 | ||

| [[#PC104_Bus|ISA_ADD_17]]/[[#GPIO| | | [[#PC104_Bus|ISA_ADD_17]]/[[#GPIO|Chip 5000406c.fpga_gpio IO 1]] | ||

| C05 | | C05 | ||

| Unused | | Unused | ||

| D05 | | D05 | ||

| [[#GPIO| | | [[#GPIO|Chip 50004054.fpga_gpio IO 2]] | ||

|- | |- | ||

| B13 | | B13 | ||

| [[#PC104_Bus|ISA_IOW]]/[[#GPIO| | | [[#PC104_Bus|ISA_IOW]]/[[#GPIO|Chip 5000406c.fpga_gpio IO 5]] | ||

| A13 | | A13 | ||

| [[#PC104_Bus|ISA_ADD_18]]/[[#GPIO| | | [[#PC104_Bus|ISA_ADD_18]]/[[#GPIO|Chip 5000406c.fpga_gpio IO 2]] | ||

| C04 | | C04 | ||

| Unused | | Unused | ||

| D04 | | D04 | ||

| [[#GPIO| | | [[#GPIO|Chip 50004054.fpga_gpio IO 1]] | ||

|- | |- | ||

| B12 | | B12 | ||

| [[#PC104_Bus|ISA_MEMR]]/[[#GPIO| | | [[#PC104_Bus|ISA_MEMR]]/[[#GPIO|Chip 5000406c.fpga_gpio IO 6]] | ||

| A12 | | A12 | ||

| [[#PC104_Bus|ISA_ADD_19]]/[[#GPIO| | | [[#PC104_Bus|ISA_ADD_19]]/[[#GPIO|Chip 5000406c.fpga_gpio IO 3]] | ||

| C03 | | C03 | ||

| Unused | | Unused | ||

| D03 | | D03 | ||

| [[#GPIO| | | [[#GPIO|Chip 50004054.fpga_gpio IO 0]] | ||

|- | |- | ||

| B11 | | B11 | ||

| [[#PC104_Bus|ISA_MEMW]]/[[#GPIO| | | [[#PC104_Bus|ISA_MEMW]]/[[#GPIO|Chip 5000406c.fpga_gpio IO 7]] | ||

| A11 | | A11 | ||

| [[#PC104_Bus|ISA_AEN]]/[[#GPIO| | | [[#PC104_Bus|ISA_AEN]]/[[#GPIO|Chip 50004040.fpga_gpio IO 0]] | ||

| C02 | | C02 | ||

| Unused | | Unused | ||

| D02 | | D02 | ||

| [[#GPIO| | | [[#GPIO|Chip 5000406c.fpga_gpio IO 9]] | ||

|- | |- | ||

| B10 | | B10 | ||

| GND | | GND | ||

| A10 | | A10 | ||

| [[#GPIO| | | [[#GPIO|Chip 50004040.fpga_gpio IO 5]] | ||

| C01 | | C01 | ||

| Unused | | Unused | ||

| D01 | | D01 | ||

| [[#GPIO| | | [[#GPIO|Chip 5000406c.fpga_gpio IO 8]] | ||

|- | |- | ||

| B09 | | B09 | ||

| 8V_48V <ref>This pin can be used to supply power to the board through the switching regulator.</ref> | | 8V_48V <ref>This pin can be used to supply power to the board through the switching regulator.</ref> | ||

| A09 | | A09 | ||

| [[#PC104_Bus|ISA_DAT_00]]/[[#GPIO| | | [[#PC104_Bus|ISA_DAT_00]]/[[#GPIO|Chip 5000405c.fpga_gpio IO 0]] | ||

| C00 | | C00 | ||

| GND | | GND | ||

| Line 239: | Line 239: | ||

|- | |- | ||

| B08 | | B08 | ||

| [[#GPIO| | | [[#GPIO|Chip 50004040.fpga_gpio IO 3]] | ||

| A08 | | A08 | ||

| [[#PC104_Bus|ISA_DAT_01]]/[[#GPIO| | | [[#PC104_Bus|ISA_DAT_01]]/[[#GPIO|Chip 5000405c.fpga_gpio IO 1]] | ||

| rowspan=8 colspan=8 | | | rowspan=8 colspan=8 | | ||

|- | |- | ||

| Line 247: | Line 247: | ||

| Unused | | Unused | ||

| A07 | | A07 | ||

| [[#PC104_Bus|ISA_DAT_03]]/[[#GPIO| | | [[#PC104_Bus|ISA_DAT_03]]/[[#GPIO|Chip 5000405c.fpga_gpio IO 3]] | ||

|- | |- | ||

| B06 | | B06 | ||

| [[#GPIO| | | [[#GPIO|Chip 50004040.fpga_gpio IO 9]] | ||

| A06 | | A06 | ||

| [[#PC104_Bus|ISA_DAT_04]]/[[#GPIO| | | [[#PC104_Bus|ISA_DAT_04]]/[[#GPIO|Chip 5000405c.fpga_gpio IO 4]] | ||

|- | |- | ||

| B05 | | B05 | ||

| N/A | | N/A | ||

| A05 | | A05 | ||

| [[#PC104_Bus|ISA_DAT_05]]/[[#GPIO| | | [[#PC104_Bus|ISA_DAT_05]]/[[#GPIO|Chip 5000405c.fpga_gpio IO 5]] | ||

|- | |- | ||

| B04 | | B04 | ||

| [[#FPGA_IRQs|FPGA IRQ 17]]/[[#PC104_Bus|TS mode DAT8]] | | [[#FPGA_IRQs|FPGA IRQ 17]]/[[#PC104_Bus|TS mode DAT8]] | ||

| A04 | | A04 | ||

| [[#PC104_Bus|ISA_DAT_02]]/[[#GPIO| | | [[#PC104_Bus|ISA_DAT_02]]/[[#GPIO|Chip 5000405c.fpga_gpio IO 2]] | ||

|- | |- | ||

| B03 | | B03 | ||

| +5V <ref name=pc1045v /> | | +5V <ref name=pc1045v /> | ||

| A03 | | A03 | ||

| [[#PC104_Bus|ISA_DAT_06]]/[[#GPIO| | | [[#PC104_Bus|ISA_DAT_06]]/[[#GPIO|Chip 5000405c.fpga_gpio IO 6]] | ||

|- | |- | ||

| B02 | | B02 | ||

| [[#GPIO| | | [[#GPIO|Chip 20a4000.gpio IO 7]] <ref>This is automatically pulsed on startup by the ts-pc104 driver as ISA_RESET</ref> | ||

| A02 | | A02 | ||

| [[#PC104_Bus|ISA_DAT_07]]/[[#GPIO| | | [[#PC104_Bus|ISA_DAT_07]]/[[#GPIO|Chip 5000405c.fpga_gpio IO 7]] | ||

|- | |- | ||

| B01 | | B01 | ||

| GND | | GND | ||

| A01 | | A01 | ||

| [[#GPIO| | | [[#GPIO|Chip 20a4000.gpio IO 8]] | ||

|} | |} | ||

<References /> | <References /> | ||

Latest revision as of 10:57, 9 April 2024

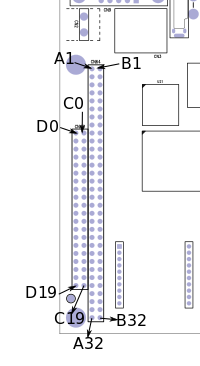

The PC/104 connector consists of four rows of pins labelled A-D. This header implements the #PC104 Bus, and optionally most pins can be GPIO.

Refer to the IO specifications for details on the IO voltages of these pins. Not all pins on the PC/104 bus are designed to be 5V tolerant, but will be in places where it is needed for compatibility with the bus.

| Pins | IO Specification |

|---|---|

| D3-D15 [1] | PCA9555 |

| A1 | CPU 3.3V |

| A10, A11, A12-A31, B6, B8, B11-B20, B25-B28, B30, D1-D2 | FPGA 3.3-V LVTTL |

| A2-A9, B4, B21-B23, C11-C18 | FPGA 3.3-V LVTTL+QS3861 |

| B2 | Open drain with pull to 5V |

- ↑ These are only present on the models with the optional I2C port expander

- ↑ Outputs a continuous 14.318180 MHz clock

- ↑ 2.0 2.1 2.2 Powering the system from PC104 5V prevents the Board's low power sleep mode from functioning.

- ↑ This pin can be used to supply power to the board through the switching regulator.

- ↑ This is automatically pulsed on startup by the ts-pc104 driver as ISA_RESET