TS-4400

| WARNING: | This manual is incomplete and is subject to change without notice while the TS-4400 is in development. |

| Product Page | |

| Documentation | |

|---|---|

| Processor | |

| 300 MHz | |

| Vortex86EX | |

| X86 Architecture | |

| Processor Page |

Overview

The TS-4400 is a TS-SOCKET System-on-Module (SoM) designed for Intel x86 instruction set and DOS compatibility. The TS-4400 uses a DMP Vortex86EX processor on the TS-SOCKET platform to provide true real-time capabilities through the use of operating systems such as FreeDOS and FreeRTOS. The computing module provides a 300 MHz x86 CPU, bootable SD media socket, onboard BootROM (BIOS), 256 megabytes of RAM, and a 22K LUT XILINX FPGA.

Getting Started

The TS-4400, being a TS-SOCKET System-on-Module, is not a standalone product. The module requires a baseboard to provide power and interface connections to the outside world. In this product manual, the TS-4400 module will be largely assumed as being paired with a TS-8551 development baseboard.

TS-8551 Mini-Manual

XXX TODO: This manual will be migrated into a full TS-8551-4400 manual of its own.

The TS-8551 is a product development baseboard designed to provide power and signal access to the TS-SOCKET System-on-Module (SoM) it hosts. The baseboard provides direct signal access to all 200 pins of the TS-SOCKET SoM. The TS-8551 baseboard also provides common interfaces such as RS232 serial on a DB9 connector, USB 2.0 Type A, two Ethernet ports, USB OTG, and embeddedTS' proprietary TS-SILO technology.

The TS-8551 has three mutually-exclusive power connector options: 5 VDC Barrel, 5 VDC screw terminal, and 8-28 VDC screw terminal. These power inputs are all controlled by a physical rocker switch. Note the TS-SILO function is on the "inside" power circuit, so while the rocker switch will interrupt external power, the TS-SILO will continue to power the system until its reserve runs out.

There are five physical jumpers on the TS-8551: SD Boot, No Charge, U-Boot, TS-4400, and SBC 5V On. When used in conjunction with the TS-4400, only the TS-4400 and No Charge jumpers are used.

The TS-4400 jumper provides the RTC VBAT signal to the CPU for software monitoring of the VBAT signal.

The No Charge jumper disables the TS-SILO functionality of the TS-8551 baseboard. This allows the system to be completely powered off instantly via the rocker switch, or by removing power from the SBC.

Connect USB Console

Console on the TS-4400 is provided from the micro USB port on the System-on-Module itself. The USB port presents itself to the host OS as a SiLabs USB to Serial adapter (Driver for most common OSes provided by SiLabs here). The serial transmissions are at 115200 baud, encoded with 8 data bits, 1 stop bit, no parity, no flow control.

Powering up

The TS-4400 system on module requires a clean regulated 5 VDC from its host baseboard. All other power sequencing activities will be handled by the SoM and will take approximately 200 ms. Once power sequencing has completed, the SBC will begin its boot sequence.

Boot Sequence

At power-on, the TS-4400 will first access the BIOS binary on the 8MB Flash chip (on-board, or on the off-board TS-9459 if present and enabled). This execution takes 300-600 milliseconds, and passes control to the DOS kernel on the first available boot device, starting with SD media, then USB media, then finally the "A:\" drive, which is an 7.4 MB Virtual Diskette located in a reserved section of the 8MB Flash chip.

Coreboot & SeaBIOS

The TS-4400 uses a version of Coreboot and SeaBIOS provided by the processor manufacturer as its BIOS and bootstrap. This binary exists within the 8MB Flash accessed during the earliest part of the CPU power-on sequence, and requires just a couple hundred milliseconds to execute before passing control to the DOS kernel.

Backup / Restore

Creating A Backup or Production Image

Restoring An Image

Cross Compiling and Development

Due to its use of the i386EX architecture, the TS-4400 is supported by many compilers and development environments. The preferred development environment for application programs on the TS-4400 is OpenWatcom 2. This once paid development environment has been made free and open-source by its original developer, and subsequently ported and updated to work in the latest Microsoft OS (Windows 10 64bit as of this writing). The most recent builds of OpenWatcom 2 are available at https://github.com/open-watcom/open-watcom-v2/releases.

Accessing The FPGA

Most functionality on the TS-4400 is implemented through the Altera Cyclone FPGA. With that in mind, the first necessity toward unlocking the TS-4400's potential is the need to understand how to talk to the FPGA.

The FPGA is connected to the CPU via the PCI bus. The first thing to do when accessing the FPGA is issue a BIOS interrupt to discover the FPGA base address. This address is assigned by the BIOS at power-up and should not be hard-coded into application software.

The example code below demonstrates a simple method for determining the base address of the FPGA:

XXX TBD: Example code here.

Development Under FreeDOS

FreeDOS is an open-source baremetal real-time MS-DOS compatible operating system designed to run legacy x86 software. embeddedTS has found FreeDOS to be an excellent, free, open-source operating system to provide DOS functionality on the TS-4400 generation of x86 products.

The FreeDOS web site includes a wealth of useful information: http://wiki.freedos.org/wiki/index.php/Main_Page

Developing software to target i386-compatible hardware can be challenging, however there are a couple open-source projects that function well under modern operating systems. embeddedTS suggests the use of Open Watcom 2.0 or one of its derivatives:

https://github.com/open-watcom

FreeDOS is a distribution of smaller tools and projects. Full information is available on their respective web sites, however the DOS kernel source code is available for download, review, and modification as necessary: https://github.com/FDOS

FreeRTOS Development

Features

Battery Backed RTC

CPU

The CPU on this product is a Vortex 86EX processor. This processor provides a computing machine that utilizes the Intel 386EX instruction set.

GPIO

The TS-4400 provides the downstream developer with 70 total FPGA-based GPIO on the PCI Express bus. TODO: Add pinout and simple DOS blinky example.

To gain access to these, first you need to get the address of the TS-4400's PCI, in specific PCIe BAR 0.

#include <bios.h> //

#include <stdio.h> // printf()

#include <conio.h> // inp() and outp()

#include <i86.h> //

#include <assert.h> // assert() used.

#include <unistd.h> // usleep()

#include "pcicfg.h"

#include "rdtsc.h"

extern int InitFlatMem(void);

extern void SetGSto4G(void);

extern uint32_t flatrealmode_readd(uint32_t addr);

#pragma aux flatrealmode_readd = \

".386p" \

"push ecx" \

"push edx" \

"push eax" \

"xor cx,cx" \

"mov gs,cx" \

"shl edx,16" \

"movzx eax,ax" \

"lea ecx,[eax+edx]" \

"pop eax" \

"pop edx" \

"mov ecx,gs:[ecx]" \

"mov ax,cx" \

"shr ecx,16" \

"mov dx,cx" \

"pop ecx" \

modify [cx] \

parm [dx ax] \

value [dx ax]

extern void flatrealmode_writed(uint32_t addr,uint32_t c);

#pragma aux flatrealmode_writed = \

".386p" \

"push edx" \

"push ebx" \

"push eax" \

"push ecx" \

"push cx" \

"xor cx,cx" \

"mov es,cx" \

"pop cx" \

"shl edx,16" \

"movzx eax,ax" \

"shl ecx,16" \

"movzx ebx,bx" \

"add ebx,ecx" \

"pop ecx" \

"mov gs:[eax+edx],ebx" \

"pop eax" \

"pop ebx" \

"pop edx" \

modify [bx cx dx] \

parm [dx ax] [cx bx]

extern uint16_t htons( uint16_t );

#pragma aux htons = \

"xchg al, ah" \

parm [ax] \

modify [ax] \

value [ax];

#define ntohs( x ) htons( x )

static inline void outpd(uint16_t port, uint32_t v);

#pragma aux outpd = \

".386" \

"shl eax, 16" \

"mov ax, dx" \

"out cx, eax" \

parm [cx] [ax dx]

uint32_t fpga_base;

uint32_t fpga_io_base;

void init4400(void) {

int i, r;

uint8_t b, d, f;

delay(10);

for (i = 0; i < 10; i++) outpd(0xc00 + (i*4), 0);

for (i = 0; i < 16; i++) inp(0x3f8);

r = pci_find(0x17f3, 0x6011, 0, &b, &d, &f); /* south bridge */ // RDC Semiconducter, ISA bridge

assert(r == 0);

/* disable usb/eth/pci irqs */

pci_cfg_write(b, d, f, 0x58, 0x0);

outp(0x4d0, inp(0x4d0) & ~0xe0); /* irq 5-7 to edge trigger */

r = pci_find(0x1172, 0x0004, 0, &b, &d, &f); /* fpga */ // Altera, undefined

fpga_io_base = pci_cfg_read(b, d, f, 0x14) & ~0x3; // do '& ~0x3' because the lowest 2 bits are statuses not part of the address.

printf("pci io at 0x%X\n", fpga_io_base);

fpga_base = pci_cfg_read(b, d, f, 0x10) & ~0xf;

printf("fpga_base at 0x%X\n", fpga_base);

r = InitFlatMem();

assert(r != 0);

}

// gpio bank in/out configuration

// is at io base + 0, 4, and 8

// for gpio 0:31, 32:63, and 64:68.

// 0 is input, 1 is output.

// output values (1 is high, 0 is low)

// gpio 0:31 are at io base + 0xc

// gpio 32:63 are at io base + 0x10

// gpio 64:68 are at io base + 0x14

void pcie_gpiotest()

{

outp(fpga_io_base + 0x0, 0xff); // FPGA GPIO bank 0 set to output.

printf("Starting square wave generation on ALL GPIO.\n");

sleep(1);

for(;;){

outp(fpga_io_base + 0xc, 0xAA); // Set GPIO 0:31 high.

outp(fpga_io_base + 0xc, 0x55); // Turn GPIO 0:31 off.

}

}

int main()

{

uint16_t i,j;

init4400();

printf("FPGA Base Address from global: 0x%X\n", fpga_base);

sleep(1);

pcie_gpiotest();

printf("Done.\n");

return 0;

}

ADC

Ethernet Port

The Ethernet port on the TS-4400 is based on the r6040pd. To load the driver and connect to Ethernet in DOS, edit the Autoexec.bat script to load and configure the driver for address 0x60 and set up the mtcpcfg file accordingly.

File: Autoexec.bat

r6040pd 0x60

echo PACKETINT 0x60 > a:\mtcp.cfg

set MTCPCFG=mtcp.cfg

dhcp

This will cause the system to start the driver and acquire a dhcp assignment during system boot.

FPGA

The FPGA on the TS-4400 is an Altera Cyclone IV EP4CGX22 connected to the CPU via the PCI bus. This part provides the majority of I/O functionality and glue logic for the TS-4400.

FPGA Registers

The FPGA's base address is returned from inquiry to the system BIOS. Once the BIOS has assigned a base address for the FPGA on the PCI bus, this table of registers will appear at the listed offset. TBD: Insert table of register functions and their address offsets.

fpga_reg_200h <= 8'h44 -- TBD Function

fpga_reg_16fh <= 8'd0 -- TBD Function

fpga_reg_202h <= 8'd0 -- TBD Function, probably RTC-related

fpga_reg_204h <= 8'd0 -- i2c, rtc mirror enable - need bitwise definition.

fpga_reg_205h <= 8'd0 -- red/grn LEDs

fpga_reg_206h <= 8'd0 -- spi flash select, lan LED, power cycle

flash select pad 1 is at 0x206 bits 2 and 3 (out enable and out value).

flash select pad 2 is at 0x206 bits 5 and 6 (out enable and out value).

power_cycle_pad_o is at 0x206 bit 7

fpga_reg_207h <= 8'd2 -- jtag ?

fpga_reg_20ah <= 8'd0 -- SPI to FPGA flash

Interrupts

LEDs

The TS-4400 has one green LED near the micro USB port. This LED will illuminate when a USB cable is connected to the module and will cease illuminating when power to the SoM is turned off. Additionally the TS-4400 has two user-specified LED outputs on CN2 pins 6 (red) and 8 (green). These are (TBD: SUBJECT TO CHANGE -- UPDATE WHEN FPGA GETS UPDATED) addressed on the ISA bus at 0x205. Bit 0 is the baseboard red LED signal, and bit 1 is the baseboard green LED signal.

Sample code:

for(;;){

// green and red leds are at 0x205.

// green is bit 1, red is bit 0.

printf("Green.\n");

outp((0x205), 2);

sleep(1);

printf("Red.\n");

outp((0x205), 1);

sleep(1);

}

Sleep

SPI

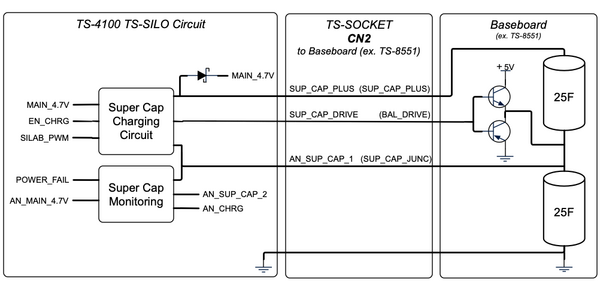

TS-SILO Supercapacitors

XXX TODO: This section needs a generic graphic or one dedicated to the TS-4400.

UARTs

This section currently contains development notes. TODO: Cleanup & flesh out.

The FPGA has up to 6 UARTs, these should behave in DOS as fairly normal serial ports:

com1_adr = 16'h3f8;

com2_adr = 16'h2f8;

com3_adr = 16'h3e8;

com4_adr = 16'h2e8;

com5_adr = 16'h3a8;

com6_adr = 16'h2a8;

USB

XXX TODO: Is this a duplicate of section 7.7?

Watchdog

External Interfaces

USB Serial Console

SD Media Socket

TS-SOCKET Connectors

| Note: | This table is a work in progress and likely contains incorrect or outdated information. |

| CN1 | CN2 | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

|

- ↑ EXT_RESET# is an input used to reboot the CPU. Do not drive active high, use open drain.

- ↑ TODO: Note on how to manipulate EN_USB_HOST_5V.

- ↑ OFF_BD_RESET# is an output from the System-on-Module that automatically sends a reset signal when the unit powers up or reboots. It can be connected to any IC on the base board that requires a reset.

- ↑ 4.0 4.1 4.2 4.3 The MAIN_5V pins should each be provided with a 5V source.

- ↑ TODO: Provide short description of FORCE_PWR_ON# function

Specifications

Power Input Specifications

Power Consumption

Power Rails

MicroSD Connector

The microSD connector enables the module to access microSD media. In FreeDOS, this media is the default C:\ boot drive.

XXX TODO: Add detail about possible baseboard SD Boot jumper and boot order. Link to proper boot order section of wiki. Add detail about maximum SD media size for supported OSes.

MicroUSB Connector

The MicroUSB connector on the TS-4400 provides a serial console connection via the SiLabs management IC on the module. This serial port communicates at 115200 baud, 8 bit data, 1 stop bit, no parity, no flow control.

Power Connectors

Power to the TS-4400 is provided exclusively through the baseboard connection to the module via the CN1 and CN2 connectors. Only the 5 V power rails are inputs. All other power rails are outputs and should not be allowed any current until such time as the SBC has finished power sequencing upon application of 5V to the power input rail.

USB Ports

The TS-4400 provides signals for two USB 2.0 ports on the CN2 header. There is one micro USB port hosted on the module itself, which exclusively provides USB Serial console access.

Revisions and Changes

FPGA Changelog

| Version | Description of changes |

|---|---|

| P.x | Prototype FPGA targeting TS-8551 baseboard. |

Microcontroller Changelog

| Version | Description of changes |

|---|---|

| P.x | Prototype |

PCB Revisions

| PCB Revision | Description of changes |

|---|---|

| Rev P.x | Prototype level x. Product under development. |

Software Images

| Version | Description of changes |

|---|---|

| P.x | Prototype image. Basic bootable FreeDOS and proof of concept FreeRTOS. |

FCC Advisory

This equipment generates, uses, and can radiate radio frequency energy and if not installed and used properly (that is, in strict accordance with the manufacturer's instructions), may cause interference to radio and television reception. It has been type tested and found to comply with the limits for a Class A digital device in accordance with the specifications in Part 15 of FCC Rules, which are designed to provide reasonable protection against such interference when operated in a commercial environment. Operation of this equipment in a residential area is likely to cause interference, in which case the owner will be required to correct the interference at his own expense.

If this equipment does cause interference, which can be determined by turning the unit on and off, the user is encouraged to try the following measures to correct the interference:

Reorient the receiving antenna. Relocate the unit with respect to the receiver. Plug the unit into a different outlet so that the unit and receiver are on different branch circuits. Ensure that mounting screws and connector attachment screws are tightly secured. Ensure that good quality, shielded, and grounded cables are used for all data communications. If necessary, the user should consult the dealer or an experienced radio/television technician for additional suggestions. The following booklets prepared by the Federal Communications Commission (FCC) may also prove helpful:

How to Identify and Resolve Radio-TV Interference Problems (Stock No. 004-000-000345-4) Interface Handbook (Stock No. 004-000-004505-7) These booklets may be purchased from the Superintendent of Documents, U.S. Government Printing Office, Washington, DC 20402.

Limited Warranty

See our Terms and Conditions for more details.