TS-7800-V2

| WARNING: | This product is about to exit the Engineering Sampling phase, meaning this documentation and the device itself have changed several times since its introduction. Force-refresh to clear the cache to view the most recent version of this documentation. Check back often; this information is subject to change as we prepare the device for mass availability. |

| |

| Product Page | |

| Product Images | |

| Specifications | |

| Documentation | |

|---|---|

| Schematic | |

| Mechanical Drawing | |

| FTP Path | |

| Processor | |

| Marvell MV88F6820 | |

| Armada 385 Arm® Cortex®-A9 1.3 GHz 32-bit Dual Core CPU |

Overview

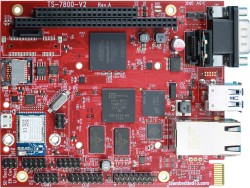

The TS-7800-V2 is a Single Board Computer (SBC) based on a Marvell MV88F6820 1.3GHz Cortex-A9 (ARMv7 architecture) Dual Core CPU. The CPU features a set of high-end peripherals such as a 10/100/1000 Ethernet, mSATA, dual USB 3.0, eMMC for onboard storage, and more. This device features WIFI, Bluetooth, an accelerometer, and an FPGA, all of which allow more DIO, UARTs, and an ISA bus to implement additional IO.

This SBC provides a migration path for customers using TS-7800 in their products. For more information, see the guide on migrating from the original TS-7800 to the updated TS-7800-V2.

Long-Term Support (LTS) Product

This platform is a part of our Long-Term Support (LTS) Program and will remain supported by up-to-date software releases throughout the lifecycle of the device. This support includes the Linux kernel, userspace utilities, as well as our board support packages (BSPs) for building complete images ready for deployment.

Our official platform lifecycle policy is stated here: https://www.embeddedts.com/about/product-lifecycle

More information about our LTS program can be found here: https://www.embeddedts.com/embeddedts-lts-support

The latest images for this product can be found in the Software Images section below.

Getting Started

A Linux workstation is recommended and assumed for development using this documentation. For users in Windows or OSX, we recommend virtualizing Linux using VMWare or similar to make the full power of Linux available. The developer should be comfortable with Linux to work with embedded Linux on the target platform. Most of our platforms run Debian, which is recommended for ease of use if there is no personal distribution preference.

The main reasons that Linux is useful are:

- Linux filesystems on the microSD card can be accessed on the PC.

- More ARM cross-compilers are available.

- If recovery is needed, a bootable medium can be written.

- A network filesystem can be served.

- Builds such as Linux kernel, Buildroot, Yocto, and distro-seed will not work from WSL1/2 on a case-insensitive filesystem.

| WARNING: | Be sure to take appropriate Electrostatic Discharge (ESD) precautions. Disconnect the power source before moving, cabling, or performing setup procedures. Inappropriate handling may cause damage to the board. |

First Linux Boot

Powering Up

5 Volts DC

| WARNING: | DO NOT CONNECT MORE THAN REGULATED 5 VOLTS DC TO THE CN4 CONNECTOR AT ANY TIME. |

The TS-7800-V2 has one primary power input location: The +5 Volt input located at CN4, immediately "behind" the DB9/DE9 serial port connector at the edge of the PCB. CN4 is populated with a screw terminal connector similar to the OSTTH020100 from On Shore Technology. This connector can be pulled off the SBC to reveal two relatively sharp connector posts. The default configuration out of the box has the screw terminal connector installed, however some shipping requests and situational events may have the SBC ship missing this connector. Check with your purchasing agent or contact the Technologic Sales Team (sales@embeddedTS.com) if the presence, or absence, of this connector is unexpected.

For most situations, power the SBC by connecting +5 Volts DC from a power supply rated for at least 12 watts with a fast slew rate. The positive and GND terminals are labeled under the connector, with the +5 V terminal being located closest to the DB9 connector. Specific applications may need more wattage depending on the final design specification.

| Note: | If custom wiring power to the screw terminal, pay VERY CAREFUL attention to the polarity of the connection. There is NO reverse-polarity protection. The positive side is the side closest to the DB9 connector, it is also noted on the PCB silk screen underneath the screw terminal connector, visible when the screw terminal plastic is pulled off. |

8-28 Volts DC

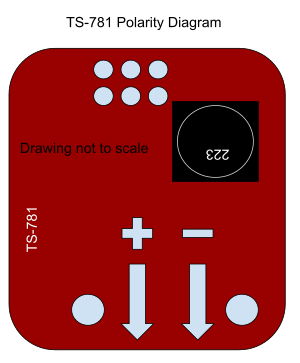

Some TS-7800-V2 models include a TS-781 power regulation card. These SBCs are sold under part numbers that include a -PS appended (for example TS-7800-V2-DMW2I-PS). On these specific SBCs, there are two places to provide power to the SBC. Note that only *ONE* of these power receptacles should be used at any time. Either the +5 V screw terminal connector covered above, OR the screw terminal connector provided by the TS-781 daughter card. If using the TS-781, the power supply connected to it should provide between 8 and 30 volts DC, with a minimum rating of 12 watts for best compatibility. The +5V connector should never be used when using the TS-781's power connector to power the SBC.

On the TS-782 power regulation board, the positive terminal is on the left hand side when facing the connector end and the coil is on the top far right corner.

Connect to the Console

Set the "EN Con" jumper, and use a null modem cable to connect the board's DB-9 connector to your workstation's COM port. Alternatively, connect a micro USB Type B cable to CN12, with the other end going to a USB port on a workstation.

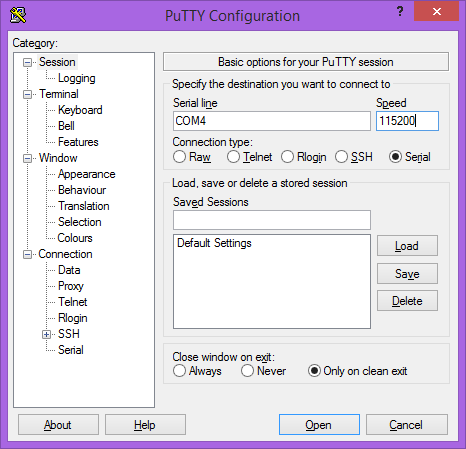

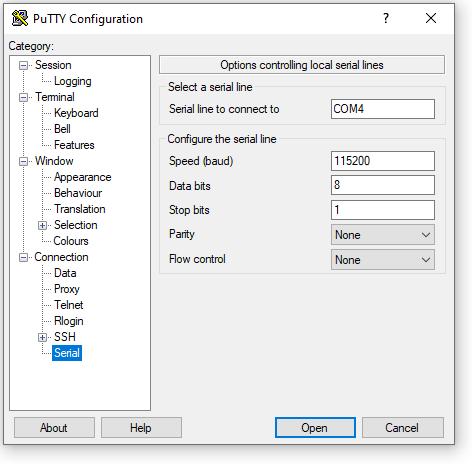

DB9 The DB9 console port comprises of RS232 serial communication at 115200 baud, no parity, 8 data bits, 1 stop bit, no handshaking, no flow control.

Micro USB The Micro USB type B port hosts a USB virtual serial port on the managing microcontroller. Some users may require the OS-appropriate driver provided by SiLabs found here: https://www.silabs.com/products/development-tools/software/usb-to-uart-bridge-vcp-drivers The TS-7800-V2 will respond over the virtual serial port at 115200 baud, no parity, 8 data bits, 1 stop bit, no handshake.

| Note: | Some terminal software will default to software flow control XON/XOFF. This setting is not compatible with the TS-7800-V2. Be sure to turn off both hardware flow control and software flow control (sometimes called "handshake") when configuring the console interface for the TS-7800-V2. |

Console from Linux

There are many serial clients for Linux, but 3 simple ones would be picocom, screen, and minicom. These examples assume that your COM device is /dev/ttyUSB0 (common for USB adapters), but replace them with the COM device on your workstation.

Linux has a few applications capable of connecting to the board over serial. You can use any of these clients that may be installed or available in your workstation's package manager:

Picocom is a very small and simple client.

picocom -b 115200 /dev/ttyUSB0

Screen is a terminal multiplexer which happens to have serial support.

screen /dev/ttyUSB0 115200

Or a very commonly used client is minicom which is quite powerful:

minicom -s

- Navigate to 'serial port setup'

- Type "a" and change location of serial device to '/dev/ttyUSB0' then hit "enter"

- If needed, modify the settings to match this and hit "esc" when done:

E - Bps/Par/Bits : 115200 8N1

F - Hardware Flow Control : No

G - Software Flow Control : No

- Navigate to 'Save setup as dfl', hit "enter", and then "esc"

Console from Windows

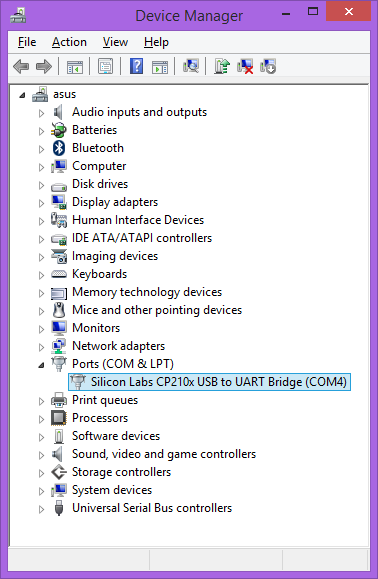

Putty is a small simple client available for download here. Open up Device Manager to determine your console port. See the putty configuration image for more details.

The TS-7800-V2 receives power through the +5VDC power connector with a 2A recommended minimum supply. Once power is applied, the device will output information via the console. The first output is from U-Boot:

U-Boot SPL 2017.09-g2113ce6a21 (Mar 06 2018 - 16:20:06) Detected Device ID 6820 (SAR1 0xCB00230D) mv_ddr: mv_ddr-armada-17.10.3-g2113ce6a21 (Mar 06 2018 - 16:20:23) DDR3 Training Sequence - Switching XBAR Window to FastPath Window mv_ddr: completed successfully Trying to boot from MMC1 force part -> 1 U-Boot 2017.09-g2113ce6a21 (Mar 06 2018 - 16:20:06 -0700) SoC: MV88F6820-A0 at 1332 MHz I2C: ready DRAM: 1 GiB (666 MHz, ECC not enabled) MMC: mv_sdh: 0 *** Warning - bad CRC, using default environment PCI: 00:01.0 - 1204:0001 - Does not fit any class Model: Technologic Systems TS-7800-V2 Found FPGA at 00.01.00 fpga_rev=0x22 board_id=0xB480 Bootflags: WDOG+ ECC- PCIE- MSATA+ SCSI: MVEBU SATA INIT SATA link 0 timeout. SATA link 1 timeout. AHCI 0001.0000 32 slots 2 ports 6 Gbps 0x3 impl SATA mode flags: 64bit ncq led only pmp fbss pio slum part sxs Net: eth0: ethernet@70000 Press ESC twice to abort autoboot in 0 second(s) Booting from the eMMC ... ** File not found /boot/boot.ub ** 18642 bytes read in 145 ms (125 KiB/s) 4796480 bytes read in 937 ms (4.9 MiB/s) ## Flattened Device Tree blob at 00100000 Booting using the fdt blob at 0x100000 Loading Device Tree to 0fff8000, end 0ffff8d1 ... OK Starting kernel ...

Note the message "*** Warning - bad CRC, using default environment" is expected unless there is a custom u-Boot configuration present. For more information on loading custom u-Boot configurations please see the Custom U-boot section.

The "SD Boot" jumper, when set, will cause U-Boot to load the kernel from eMMC and then boot to SD, and when unset, U-Boot will load the kernel from eMMC and boot to eMMC.

| Note: | The "*** Warning - bad CRC, using default environment" can be safely ignored. This indicates that u-boot scripts are not being customized. Typing "env save" will hide these messages, but this is not needed. |

U-Boot Environment

The U-Boot environment on the TS-7800-V2 is stored in the on-board eMMC flash.

# Print all environment variables

env print -a

# Sets the variable bootdelay to 5 seconds

env set bootdelay 5;

# Variables can also contain commands

env set hellocmd 'led red on; echo Hello world; led green on;'

# Execute commands saved in a variable

env run hellocmd;

# Commit env changes to the spi flash

# Otherwise changes are lost

env save

# Restore env to default

env default -a

# Remove a variable

env delete emmcboot

U-Boot Commands

# The most important command is

help

# This can also be used to see more information on a specific command

help i2c

# Boots into the compressed binary at $loadaddr.

bootz

# Boots into the compressed binary at $loadaddr, specifies the fdtaddr

# so Linux knows where to find the board device-tree

bootz ${loadaddr} - ${fdtaddr}

# Get a DHCP address

dhcp

# This sets ${ipaddr}, ${dnsip}, ${gatewayip}, ${netmask}

# and ${ip_dyn} which can be used to check if the dhcp was successful

# These commands are used for scripting:

false # do nothing, unsuccessfully

true # do nothing, successfully

# This command lets you set fuses in the processor

# Setting fuses can brick your board, will void your warranty,

# and should not be done in most cases

fuse

# This command is used to copy a file from most devices

# Load kernel from SD

ext4load mmc 1:2 ${loadaddr} /boot/zImage

# Load Kernel from eMMC

ext4load mmc 0:2 ${loadaddr} /boot/zImage

# You can view the fdt from u-boot with fdt

ext4load mmc 0:2 $fdtaddr /boot/armada-38x.dtb

fdt addr ${fdtaddr}

fdt print

# You can blindly jump into any memory

# This is similar to bootm, but it does not use the

# u-boot header

ext4load mmc 0:2 ${loadaddr} /boot/custombinary

go ${loadaddr}

# Browse fat,ext2,ext3,or ext4 filesystems:

ext4ls mmc 0:1 /

# Access memory like devmem in Linux, you can read/write arbitrary memory

# using mw and md

# write

mw 0x10000000 0xc0ffee00 1

# read

md 0x10000000 1

# Test memory.

mtest

# Check for new SD card

mmc rescan

# Read SD card size

mmc dev 1

mmcinfo

# Read eMMC Size

mmc dev 0

mmcinfo

# The NFS command is like 'load', but used over the network

dhcp

env set serverip 192.168.0.11

nfs ${loadaddr} 192.168.0.11:/path/to/somefile

# Test ICMP

dhcp

ping 192.168.0.11

# Reboot

reset

# Delay in seconds

sleep 10

# You can load HUSH scripts that have been created with mkimage

ext4load mmc 0:1 ${loadaddr} /boot/ubootscript

source ${loadaddr}

# Most commands have return values that can be used to test

# success, and HUSH scripting supports comparisons like

# test in Bash, but much more minimal

if load mmc 1:1 ${fdtaddr} /boot/uImage;

then echo Loaded Kernel

else

echo Could not find kernel

fi

# Commands can be timed with "time"

time bdinfo

# Print U-boot version/build information

version

Updating U-Boot

There is a very small possibility that during development it becomes necessary to update the U-Boot binary, either due to a published bug fix or very low-level implementation by the down-stream developer. The U-Boot binary resides in a read-only protected portion of the eMMC device on the TS-7800-V2. To write a new U-Boot binary, this part of the chip must be write-enabled in Linux.

echo 0 > /sys/block/mmcblk0boot0/force_ro

dd if=u-boot-spl.kwb of=/dev/mmcblk0boot0

sync

echo 1 > /sys/block/mmcblk0boot0/force_ro

WARNING: If this process fails, DO NOT REBOOT. If the mmcblk0boot0 partition does not contain a valid u-boot binary during boot, the SBC will fail to boot. This means it is VERY possible to brick the SBC in the attempt to update U-Boot. Technologic Systems strongly advises this activity should only be undertaken if there is no other means of achieving a needed functionality.

Modify Linux Kernel cmdline

The Linux kernel cmdline can be customized by modifying the cmdline_append variable. The variable contents are clobbered when set, so be sure to specify the full desired cmdline string.

env set cmdline_append console=ttyS0,115200 init=/sbin/init quiet

env save

The kernel command line can also be modified from from the on-board Linux. Debian (and other distributions) provide a U-Boot utilities package that contains the tools necessary to create a U-Boot script:

apt-get update && apt-get install u-boot-tools -y

echo "env set cmdline_append console=ttyS0,115200 init=/sbin/init quiet" > /boot/boot.scr

mkimage -A arm -T script -C none -n 'boot script' -d /boot/boot.scr /boot/boot.ub

The boot.scr includes the plain text commands to be run in U-Boot on startup. The mkimage tool adds a checksum and header to this file which can be loaded by U-Boot. The .ub file should not be edited directly.

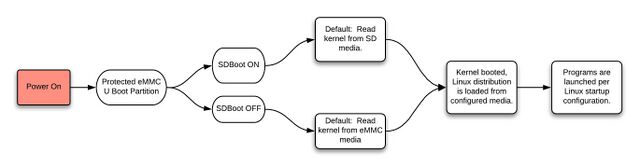

Boot Paradigms

U-Boot is always loaded from the onboard eMMC boot partitions (/dev/mmcblk0boot*). U-boot can access the eMMC, SATA, Network, and USB. By default it will load Linux from the first partition on the eMMC, but it can be configured to boot to SATA, USB, or Network by default. When the U-Boot jumper is present the board will attempt to boot to USB for our #Production Mechanism.

The eMMC and SD cards shipped with the unit are pre-programmed with our Debian Stretch image.

Booting to U-Boot

The U-Boot bootloader resides in a special, protected, part of the eMMC chip that is normally read-only to the operating system. When the SBC is powered on, the processor will load u-boot from this protected eMMC section and launch into U-Boot execution. If the physical jumper labeled U-Boot is installed (with no bootable USB media present), the SBC will then stop at the U-Boot shell and await further user interaction.

Booting From USB

With the U-Boot jumper installed, the SBC will automatically look for bootable media on USB and attempt to boot that media. If no bootable USB media is present, the SBC will drop to the U-Boot prompt and await further instruction via the console.

Booting From eMMC

Without the "SD Boot" jumper, the default U-Boot behavior will attempt to mount and load the kernel from the first available regular partition on eMMC. The kernel will then load essential driver functionality, properly mount necessary filesystems, and begin execution of the Debian environment.

Booting From SD

With the "SD Boot" jumper populated, the default U-Boot behavior attempt to mount and load the kernel from the first available regular partition on the SD media. The kernel will then load essential driver functionality, properly mount necessary filesystems, and begin execution of the Debian environment.

Changing Boot Paradigm / Booting from SATA

The TS-7800-V2 can automatically boot from any recognized bootable media. The default TS-7800-V2 U-Boot environment provides for automatic booting from USB, SD, and eMMC. The downstream developer may alternatively choose to boot from SATA or network. The pre-defined boot scripts in U-Boot include:

usbboot

emmcboot

sdroot

nfsboot

sataboot

Any of these commands can be swapped for another in the bootcmd script. Editing the bootcmd script is the same procedure as modifying the kernel command line:

setenv bootcmd 'if test ${jpsdboot} = ' \''on'\' '; then run sataboot; else run emmcboot; fi;'

env save

If the ability to change boot modes based on the SDBOOT jumper is not needed, the above script can be simplified significantly:

setenv bootcmd run sataboot;

env save

Jumper Configuration

| Jumper | Function |

|---|---|

| SD Boot | Boot to SD if populated, otherwise boot to eMMC. |

| EN Console | Enables the console, when populated, ttts9 is TTL on PC104 pins 14 and 15. When depopulated, ttts9 is on DB9 pins 2 and 3, replacing console RS232. |

| U Boot | Boots to USB if present (see Production Mechanism). Stops boot in u-boot rather than booting to the disk image if no USB present. |

Boot Flags

Some features of the board can only be configured in early boot. These behaviors can be changed from Linux using the ts7800ctl.

| Bit | Description |

|---|---|

| 7 | Reserved |

| 6 | 1 = Enable ECC and only use one chip

0 = Use both chips as RAM |

| 5:1 | Reserved |

| 0 | 1 = Enable watchdog by default

0 = Disable watchdog |

Bit 6 controls whether ECC is enabled or not. The default builds of the TS-7800-V2 use two 512MB DDR3 chips, and ECC is enabled by dedicating one of those chips to ECC. This will split the usable RAM in half, but allow auto correction of single bit errors, or detection of double bit errors.

Bit 0 allows disabling the watchdog right out of reset. This only enables whether it is enabled on power on, but the default u-boot will start feeding the watchdog as soon as it starts. To completely disable the watchdog later software would need to not feed the watchdog, or stop feeding and send a byte to turn off the watchdog. See the #Watchdog section for more information.

On startup u-boot will print out: Model: Technologic Systems TS-7800-V2

fpga_rev=0x1B board_id=0xB480 Bootflags: WDOG+ ECC- PCIE- MSATA+ SCSI: MVEBU SATA INIT SATA link 0 timeout.

This bootflags shows which boot flags are enabled/disabled. To modify these, use ts7800ctl from Linux.

# Default boot strapping. Disables ECC, enables mSATA and WDOG

ts7800ctl -A 7 -D 0x1

# Enable ECC, enable mSATA and WDOG

ts7800ctl -A 7 -D 0x41

# Disable ECC, Enable PCIe and WDOG

ts7800ctl -A 7 -D 0x81

ts7800ctl

The ts7800ctl utility allows the downstream developer access to core functionalities in the microcontroller, FPGA, CPU, and other hardware features of the TS-7800-V2 not specifically supported by other common Linux software.

Usage: ts7800ctl [OPTION] ...

Examine/Modify state of TS-7800-V2 hardware.

General options:

-s seconds Number of seconds to sleep for

-r CHANS Sample ADC channels CHANS, e.g. "0-2,4", "1,3,4"output raw data to standard out

-S CHANS Sample ADC channels CHANS, e.g. "0-2,4", "1,3,4"output string parseable data to standard out

-n Red LED on

-F Red LED off

-g Green LED on

-G Green LED off

-i Display board info

-o Display one time programmable data

-m Display contents of non-volatile memory

-a[N] Display accelerometer data, loop N times (0=forever)

-t Display board temperature

-A ADDR Write DATA to ADDR in non-volatile memory

-D DATA Write DATA to ADDR in non-volatile memory

-M[xx:xx:xx:xx:xx:xx] Display [or optionally set] the MAC address

-O Display odometer(hrs board has been running for)

-l RATE Set CPU clock rate, or if no argument lists possible rates (max default)

-c CORES Set 1/2 Cores (max default)

-V Verbose output

Running ts7800ctl -i will output useful status information about the current running state of the TS-7800-V2. The output will be in this format:

model=7800

buildmodel=TS-7800-V2-DMN1I

max_rate=1333

max_cores=2

pcbrev=a

fpga_rev=0x2D

silabs_rev=7

board_id=0xB480

pclk=1333

nbclk=667

hclk=333

dclk=667

refclk=25

cpu_temp=71309

cpu_core=1264

ram_1350=1472

v_1200=1281

v_1800=1779

v_8_30=1140

v_5va=5260

an_3300=3354

temp_sens=53959

hwaddr=e8:1a:58:00:04:eb

Sleep

The TS-7800-V2 can enter a very low-power sleep state to assist in power management. This state effectively will power the main components (CPU, RAM, storage, peripherals, etc.) completely off, leaving just a low-power management chip counting an internal timer while waiting for the power-up signal. Power drawn while in this state is documented here. Sleep is a timed function of the management IC. When used, the sleep command is given a number of seconds to hold the device in low-power mode before causing it to boot again. This is the default functionality. This timer can be interrupted at any time by pulling either DIO_04 or ISA_B32 to 3.3 V for 100 milliseconds.

| Note: | Issuance of the sleep command is the equivalent of an immediate power loss. Doing this during otherwise normal operation can cause filesystem corruption and data loss. It is advised to properly perform Linux shutdown tasks, or at least remount all write-able media into a read-only state before issuing the sleep command. |

Backup / Restore

While all of our products ship with images pre-loaded in to any supplied media, there are many situations where new images may need to be written. For example, to restore a device to its factory settings or apply a customized image/filesytem for application deployment. Additionally, specific units may be used for development and that unit's disk images need to be replicated to other units to be deployed in the field.

We offer a number of different ways to accomplish both capturing images to be written to other units, and the actual writing process itself. See the sections below for details on our USB Image Replicator tool to capture and/or write images, as well as details on manual processes to capture and write images on each of this device's media.

Image Replicator

This platform supports our Image Replicator tool. The Image Replicator tool is intended for use by developers as a means to write bootable images or filesystems onto a device's media (SD / eMMC / SATA / etc.) as part of the developer's production or preparation process. In addition to writing media, the Image Replicator tool can capture images from a device's media and prepare them to be written to other devices.

The Image Replicator tool is a USB disk image that boots from a target device to capture or write USB drive-resident media directly onto the target without a host workstation. It runs from a USB drive and allows:

- Capturing an image of the device storage (eMMC/microSD)

- Writing an existing image back to media

- Creating bootable media for mass deployment

The USB disk image is based on Buildroot and contains a set of scripts that handle the capture and write processes. The processes and scripts are flexible, can be used as-is, or adapted into larger production processes to format and load data onto devices. A single USB drive can be used to capture images from a device and then, once inserted in to other devices, write those same images onto other devices. The capture process is not necessary if it is not needed. Images for the target device can be copied to the USB drive, booted on compatible units, and have the target images written to that unit's media.

Image Capture Process

The image capture process performs the following steps. For more detailed information, see the Image Capture section below.

- If no valid images exist on the disk, image capture starts.

- For each valid media present on the unit, a bit for bit copy of the source is made.

- This image is mounted, sanitized (to remove unneeded files and allow safe copying of the image to other units), and saved as either a disk image or a tarball, depending on the partition layout of the source disk.

- All images and tarballs are compressed, with both the output files' MD5 hash saved, as well as all of the files contained in the root partition (MD5 hashes saved) to a file for later verification.

The captured images and tarballs are named such that the USB Image Replicator disk can be immediately used to boot another unit and have it perform the Image Write process, writing that unit's media with the captured images.

| Note: | When using this process, the USB drive used for the Image Replicator must be sized large enough to handle multiple compressed images as well as the uncompressed copy of an active media image. If the image capture process runs out of space, the process indicates a failure. |

Image Write Process

The image write process performs the following steps. For more detailed information see the Image Write section below.

- For each valid media present on the unit, find the first valid source image file for it.

- If a source image exists for a media that is not present on the unit, then the process indicates a failure.

- If the source image is a tarball, format the target disk with an appropriate file system and unpack it to the target disk, verifying all files against the MD5 hash file list after they are written.

- If the source image is a disk image, write that to the target disk. If an MD5 file for the disk image exists, read back the written disk and compare it to the hash.

Creating a USB Image Replicator Disk

Image Replicator USB disk images can be found below:

Disk image: ts7800v2-usb-image-replicator.dd.xz

Tarball: ts7800v2-usb-image-replicator-rootfs.tar.xz

Two types of USB Image Replicator images are available for this platform: a tarball and an actual disk image. They both have the same contents yet provide different methods to write the Image Replicator tool to a USB disk.

- Disk Image (.dd.xz)

- The disk image is easier to write from different workstation OSes, will auto-expand to the full disk length on its first boot, and is intended to be used for image capture (and later image writing) due to its small size and auto-expansion process. We recommend this route for users who may not have access to a Linux workstation or need to capture images from a golden unit first.

- Tarball Image (.tar.xz)

- The tarball image is easiest to write from a Linux workstation, but requires creating a partition table on the USB disk (if one does not already exist), formatting the filesystem, and unpacking the tarball. It can readily be used for both image capture and writing, but is easiest when image capture is not needed, due to the auto-expansion process.

| Note: | This process recommends a solid-state USB drive. Slower USB drives, especially those with spinning media, may take too long to enumerate and the bootloader will not boot the Image Replicator disk. Low quality, damaged, and/or worn out USB drives may cause unexpected errors that appear unrelated to the USB drive itself. If there are issues using the Image Replicator, we recommend first trying a new, fresh, high-quality USB drive from a trusted brand. |

Disk Image

This process uses a small disk image that can be written to a USB device. This disk image uses an ext3 filesystem which expands on its first boot to the full length of the disk before beginning the image capture process, and is recommended for users who may not have access to a Linux workstation or who need to capture images from a golden unit.

It is possible to use the disk image only for image writing. However, to ensure that full disk space is available, it is recommended to write the disk image to a USB drive, set the IR_NO_CAPTURE_* Image Replicator Runtime Options, boot it on the target unit, let the system boot and expand to the disk, insert the USB drive back in to a workstation, and then copy in the desired image files for the target unit from the workstation.

Writing Disk Image From a Linux Workstation

The disk image can be written via the command line with the dd command (replace /dev/sdX with the correct USB device node):

xzcat <platform>-usb-image-replicator.dd.xz > /dev/sdX

Graphical tools also exist for this purpose, for example balenaEtcher[1] offers this functionality.

Writing Disk Image From a Windows Workstation

A number of tools exist for writing an image to a USB drive, including (but not limited to) balenaEtcher[1] and Win32DiskImager[2]

Writing Disk Image From a MacOS Workstation

We recommend using a tool such as balenaEtcher[1] to write disk images.

Tarball

This process is easiest on a Linux workstation, but can be performed on other operating systems so long as they can support a compatible filesystem, the xz compression algorithm, as well as the tarball archive format. Note that in many cases, one of our computing platforms running our stock Linux image can be used if a Linux workstation is not available. After writing the tarball to a USB disk, the full length of the USB disk would be available to copy source images, to write them to other units.

The image replicator and scripts require a minimum of 50 MB. Additionally, the size of target disk images or tarballs used also dictate the minimum USB disk size required. The USB drive should have only a single partition, which is formatted ext2[1] / 3 / 4[2] or FAT32/vfat[3] Note that other filesystems are not compatible with U-Boot and therefore cannot be used.

Writing Tarball From a Linux Workstation

# This assumes USB drive is /dev/sdc:

sudo mkfs.ext3 /dev/sdc1

sudo mkdir /mnt/usb/

sudo mount /dev/sdc1 /mnt/usb/

sudo tar --numeric-owner -xf /path/to/<platform>-usb-image-replicator-rootfs.tar.xz -C /mnt/usb/

sudo umount /mnt/usb/

Writing Tarball From a Windows Workstation

A third party tool is recommended, as native Windows archive tools have occasionally not worked correctly. Tools such as 7-Zip[4] or PeaZip[5] are known working. (It may also be possible to use Windows Subsystem for Linux following the Linux Workstation instructions above, but this has not been tested.)

Note that some Windows tools may attempt to use the whole disk, rather than create a partition table. A partition table with a single partition is required for U-Boot support.

With a formatted USB disk, the archive can be unpacked to the root folder of the USB disk. Be sure to not unpack the tarball contents into a new folder on the drive, as this will not boot.

- ↑ The ext2 filesystem has a max file size limit as low at 16 GiB. This may cause issues for Image Capture.

- ↑ . Use of ext4 may require additional options. U-Boot on some platforms does not support the 64-bit addressing (added as default) in recent revisions of

mkfs.ext4. If using e2fsprogs 1.43 or newer, the options-O ^64bit,^metadata_csummay need to be used with ext4 for proper compatibility. Older versions of e2fsprogs do not need these options passed, nor are they needed for ext2 / 3. - ↑ . The FAT32 (supported by vfat in Linux) filesystem has a max file size limit of 4 GiB. This may cause issues for Image Capture.

- ↑ embeddedTS is not affiliated with this tool. 7-Zip 21.07 tested in Windows 10 on 20220222

- ↑ embeddedTS is not affiliated with this tool. PeaZip 7.2.0 tested in Windows 10 on 20220222

Running the Image Replicator Tool

U-Boot on the TS-7800-V2 will attempt to boot from an attached USB disk if the U-Boot jumper is set. This is the mechanism to boot either of the two disk images on the TS-7800-V2.

Once a USB drive is formatted with the Image Replicator tool (see Creating a USB Image Replicator Disk for the correct files and process), boot to this USB drive (note that the Image Replicator already sets up the correct U-Boot boot scripts to boot to the USB drive, see the aforementioned section for details on how to make U-Boot call the scripts on the USB drive). This will start either image capture if no disk images/tarballs are present on the USB drive, or image write if there are disk images/tarballs present on the USB drive.

Image Replicator Runtime Options

Some of the runtime operations of the Image Replicator can be specified. These are handled by creating empty files in the root folder of the bootable USB drive. When booted, these files are analyzed and actions taken based on them.

| Option | Description |

|---|---|

|

|

When capturing, skip media-matching this name. See the respective platform manual for information on which names correspond to which physical media. Note that the names are generic and match what the media is captured as, regardless of actual device node. The names are uniform between capture and write for a given system. |

IR_NO_COMPRESS

|

When capturing, do not compress the data. On slower systems, slower disks, or systems with a large amount of data to capture, the final compression can take a significant amount of time. This option will allow a capture, but will not attempt to compress it. |

IR_SHELL_ONLY

|

When booting, skip doing any of the image replication process (Capture or Write) and instead drop to a login prompt. Useful for debugging. Note that, to prevent any confusion the system will indicate a non-critical failure when skipping any of the Image Replication process. |

Image Replicator LED Status

The green and red LEDs of the platform are used to indicate status.

Any LED patterns not matching the table below indicate different operational states of the platform itself, e.g. executing the bootloader, the kernel is running but Image Replicator has not yet started, etc.

| Green | Red | State | Description |

|---|---|---|---|

| Short Strobe | Solid | Running | The Image Replicator process is running. |

| 0.5 Hz Blink | Off | Succeeded | All operations being performed by the Image Replicator have completed successfully. |

| Off | 0.5 Hz Blink | Non-critical Failure | One or more operations being performed by the Image Replicator have failed to complete. View logs in /tmp/logs/ as well as the failure reason in /tmp/failed

|

| Off | 4 Hz Blink | Critical Failure | An operation has failed in a way that could leave the device inoperable if power were to be removed. View logs in /tmp/logs as well as the failure reason in /tmp/failed.

|

Image Capture

If no valid images to write exist on the booted USB Image Replicator drive, the image capture process starts automatically.

Note that while in progress, the USB Image Replicator drive is mounted read-write. Do not remove power or disconnect the USB Image Replicator drive until the whole process has completed.

To help diagnose failures, files in /tmp/logs/ contain output from each capture process.

For each media present on the unit (SD / eMMC / SATA / etc.), the image capture process will do the following:

- Copy the entire media image to an appropriately named file on the USB Image Replicator drive, e.g.

sdimage.dd. No data is written to the source media and it is never mounted. The source disk can follow the stock partition layout, or implement a customized one. - Perform an fsck on the Linux rootfs partition in the image file. Note that, if deviating from the standard partition layout, it may be necessary to modify the scripts handling the capture process.

- Mount the Linux rootfs partition from the image file and sanitize the filesystem. The sanitization process removes temporary files (e.g.

/log/files), unique files (e.g. ssh private key files, machine ID files), adds a file to indicate that it is a custom image with the date as its contents, etc. The full list of operations can be found in this script. It may be necessary to modify this file for unique situations. - If the media's partition layout uses only a single partition, the filesystem is packed in to a tarball on the USB Image Replicator drive which is appropriately named and compressed, e.g.

sdimage.tar.xz. The image file is then unmounted and removed from the USB Image Replicator drive. - If the media's partition layout uses multiple partitions, the image file is then unmounted, an md5sum of the image file taken, compressed and appropriately named on the USB Image Replicator drive, e.g.

emmcimage.dd.xz, and then an md5sum of the compressed image is taken.

Note that when using this process, the USB Image Replicator drive that is used must be sized large enough to handle multiple compressed images as well as the uncompressed copy of the media image actively being worked with. If the image capture process runs out of space, the process will indicate a failure via the LEDs.

The images files captured are saved to the root folder of the USB Image Replicator drive. Upon completion, it is safe to remove power or unplug the USB drive.

For more details on the image capture process, see this script.

Image Write

This process is used to write existing images to media on a target unit. If appropriately named disk images or tarballs (see table below) are present in the root folder of the USB Image Replicator drive when booted, then the startup scripts will start the image writing process. The latest disk images we provide for our platforms can be downloaded from our FTP site, see the backup and restore section for links to these files.

Note that the USB Image Replicator drive remains read-only through the entire process but target devices may be mounted or actively written. It is not advised to remove power or disconnect the USB Image Replicator drive until the whole process has completed.

To help diagnose failures, files in /tmp/logs/ contain output from each writing process.

The Image Replicator script expects disk images or tarballs to have specific names to match the target media. The script will attempt to match tarball and then disk image names (in the order they are listed in the table below) for each target media, using the first file that is found to write to the target media. Note that symlinks can be used on the USB Image Replicator disk if formatted with a filesystem that supports symlinks. This can be used, for example, to write the same tarball to both SD and eMMC from only a single copy of the source tarball.

Upon completion, it is safe to remove power or unplug the USB drive.

For more details on the image write process, see this script.

The following table is the list of valid file names and how they are processed:

| Target media | Accepted filenames | Description |

|---|

| SD Card |

|

Tar of the filesystem. This will repartition the SD card to a single partition and extract this tarball to the filesystem. If present, a file named /md5sums.txt in the tarball will have its contents checked against the whole filesystem after the tarball is extracted. This md5sums.txt file is optional and can be omitted, but it must not be blank if present. This file is present in our official images and is created during image capture with the Image Replicator tool.

|

|---|---|---|

|

|

Disk image of the media. This will be written to the SD card block device directly. If present on the USB Image Replicator drive, a file named /sdimage.dd.md5 will be used to verify the data written to the SD card against this checksum. This file is provided with our official images and is created during image capture with the Image Replicator tool.

|

| eMMC |

|

Tar of the filesystem. This will repartition the eMMC to a single partition and extract this tarball to the filesystem. If present, a file named /md5sums.txt in the tarball will have its contents checked against the whole filesystem after the tarball is extracted. This md5sums.txt file is optional and can be omitted, but it must not be blank if present. This file is present in our official images and is created during image capture with the Image Replicator tool.

|

|---|---|---|

|

|

Disk image of the media. This will be written to the eMMC block device directly. If present on the USB Image Replicator drive, a file named /emmcimage.dd.md5 will be used to verify the data written to the SD card against this checksum. This file is provided with our official images and is created during image capture with the Image Replicator tool.

|

| SATA |

|

Tar of the filesystem. This will repartition the first SATA drive with a single partition and extract this tarball to the filesystem. If present, a file named /md5sums.txt in the tarball will have its contents checked against the whole filesystem after the tarball is extracted. This md5sums.txt file is optional and can be omitted, but it must not be blank if present. This file is present in our official images and is created during image capture with the Image Replicator tool.

|

|---|---|---|

|

|

Disk image of the media. This will be written to the first SATA block device directly. If present on the USB Image Replicator drive, a file named /sataimage.dd.md5 will be used to verify the data written to the SD card against this checksum. This file is provided with our official images and is created during image capture with the Image Replicator tool.

|

| U-Boot |

|

U-Boot binary blob. This will be written to the bootloader area of eMMC. If the file /u-boot.kwb.md5 is present on the USB drive, this will be used to verify the data written to disk.

|

|---|

Building the Image Replicator from Source

The Image Replicator tool uses Buildroot to create the bootable USB disk image and tarball. See the project repository on github for information on compatibility and instructions on building: https://github.com/embeddedTS/buildroot-ts

Backup/Restore SD Card

| Note: | Our Image Replicator tool can be used to automate this process. |

MicroSD is a storage media ubiquitous to embedded computing. When sourced through authorized distribution its characteristics can be very consistent and reliable across a product line. Combined with a good backup/restore strategy, hardware deployments can be simplified to a handful of commands resulting in a finished product with minimal effort.

The current shipping image tarball is located here.

| Note: | Only either the full-size SD card, or the micro SD card may be present on the TS-7800-V2. Attempting to use both interfaces at the same time will result in corruption on both media. |

Using a TAR archive is the preferred method for moving mass data to or from filesystems on the TS-7800-V2. This method allows for significant variations in media size without the need to calculate and modify image size based on specific media characteristics. So long as the data fits on the media, the "image file" does not need to be specially tailored to the target media.

Preparing the Media

This step may or may not be necessary, depending on the filesystem status of the target media. EXT3 and EXT4 are used interchangeably in this document because the TS-7800-V2 supports both. EXT4 is newer and generally considered better, but ext3 is more compatible across a variety of other systems. Care should be taken to ensure these commands are pointed at the correct device: Accidentally using the wrong device node with these commands could cause catastrophic data loss.

umount /dev/mysdcard1

mkfs.ext4 /dev/mysdcard1

Performing the backup/restore

| Note: | Our Image Replicator tool can be used to automate this process. |

From Workstation

---

Restore

Note this example uses generalities to describe the path to an SD card, and presumes root access (meaning 'sudo' may be necessary, depending on the particular OS). Replace 'mysdcard1' and 'mountpoint' with names appropriate to your specific situation.

mkdir mountpoint

mount /dev/mysdcard1 mountpoint

tar -xJf ts7800v2-deb_stretch-latest.tar.xz -C mountpoint/ --numeric-owner # note the capital letters J and C in this command line: These are important.

umount mountpoint

sync

Back Up Note general terminology and paths are used in this example. Replace general terms with those specific to your computing platform.

mkdir mountpoint

mount /dev/mysdcard1 mountpoint

cd mountpoint

tar -cJf ../mysdcard_backup.tar.xz * --numeric-owner #note the capital J in this line: It is important.

sync

cd .. && umount mountpoint

From TS-7800-V2

Boot the TS-7800-V2 to eMMC, USB, or SATA.

Use the instructions above. The SD card's first partition on the TS-7800-V2 is defined as /dev/tssdcarda1.

Backup/Restore eMMC

The TS-7800-V2 eMMC media backup and restore process must be performed while the TS-7800-V2 is booted from a separate media resource. There are several possible devices. These instructions will focus largely on USB and SATA media, but any other possible boot media could be used instead (eg. Network boot or micro SD). This is the preferred backup/restore method.

| Note: | These instructions include commands that will erase target media. Be careful not to accidentally erase the wrong media. |

Preparing the backup media

Use Linux PC to install image onto 8GB or greater USB media (or SATA).

Prepare the transfer media using the Linux PC:

wget ftp://ftp.embeddedTS.com/ts-arm-sbc/ts-7800-v2-linux/distributions/ts7800v2-deb_stretch-latest.tar.xz

sudo mkdir mount

sudo mkfs.ext4 /dev/your_usb_or_sata_drive_partition_1 #this erases the media - make sure it doesn't have anything you want to keep on it!

sudo mount /dev/your_usb_or_sata_drive_partition_1 mount

cd mount

sudo tar -xJf ../ts7800v2-deb_stretch-latest.tar.xz -C . --numeric-owner

sudo cp ../ts7800v2-deb_stretch-latest.tar.xz root/

cd ..

sync

sudo umount mount

Backing up eMMC

| Note: | Our Image Replicator tool can be used to automate this process. |

This backs up the data partition of the eMMC device -- note this backup does NOT include uBoot or any other special partitions.

Be sure the backup media has sufficient free space.

Populate the U BOOT jumper. Install backup media. Power on SBC.

#at U-Boot prompt, if USB media was used:

run usbboot

#at U-Boot prompt, if SATA media was used:

run sataboot

#Debian will load from the selected media.

#Log in as root, no password is required.

mkdir mount

mount /dev/mmcblk0p1 mount

cd mount

tar -cJf ../emmcBackup.tar.xz -C . --numeric-owner * #this will take a while. Note the capital J.

sync

cd ..

umount mount

shutdown -h now

Once the SBC indicates it has halted, remove power from the SBC and disconnect your backup media, the backup file is at "/root/emmcBackup.tar.xz" on the backup media.

Restoring eMMC

| Note: | Our Image Replicator tool can be used to automate this process. |

Remove the media from the PC and install it onto the TS-7800-V2.

Populate the U BOOT jumper.

Use the media to install the new image onto the eMMC on the TS-7800-V2:

#at U-Boot prompt, if USB media was used:

run usbboot

#at U-Boot prompt, if SATA media was used:

run sataboot

#debian loads from selected media.

#login as root, there is no password required.

umount /dev/mmcblk0p1 mount

mkfs.ext4 /dev/mmcblk0p1 #note: This step erases the eMMC user data partition.

mount /dev/mmcblk0p1 mount

cd mount

tar -xJf ../ts7800v2-deb_stretch-latest.tar.xz -C . --numeric-owner

Debian

Debian 13 - Trixie

Debian 13 - Getting Started

This Debian release is available in 2 flavors with various packages. See our Debian releases in the Software Images section for links to the latest images available.

| Image | Description |

|---|---|

| Headless |

|

| Minimal |

|

The default login is root with no password.

Debian 13 - Networking

The network in Debian is configured with /etc/network/interfaces. For complete documentation, see Debian's documentation here

Some common examples are shown below. On this release network interfaces follow the predictible network interface names. Run ip addr show to get a list of the network interfaces.

Most commonly:

- end0 - Ethernet device 0 (CPU Ethernet)

- enp1s0 - Ethernet PCIe port 1 slot 0 Ethernet

- usb<mac> - USB Ethernet

- wlan0 - Wi-Fi

DHCP on end0. Create the file /etc/network/interfaces.d/end0 with the contents:

allow-hotplug end0 iface end0 inet dhcp

Static IP on end0. Create the file /etc/network/interfaces.d/end0 with the contents:

allow-hotplug end0

iface end0 inet static

address 192.0.2.7/24

gateway 192.0.2.254

These will take effect on the next boot, or by restarting the networking service:

service networking restart

Debian 13 - Wi-Fi Client

Wireless interfaces are also managed with configuration files in /etc/network/interfaces.d/. For example, to connect as a client to a WPA network with DHCP. Note some or all of this software may already be installed on the target.

Install wpa_supplicant:

apt-get update && apt-get install wpasupplicant -y

Run:

wpa_passphrase youressid yourpassword

This command will output information similar to:

network={

ssid="youressid"

#psk="yourpassword"

psk=151790fab3bf3a1751a269618491b54984e192aa19319fc667397d45ec8dee5b

}

Use the hashed PSK in the specific network interfaces file for added security. Create the file /etc/network/interfaces.d/wlan0 with the contents:

allow-hotplug wlan0

iface wlan0 inet dhcp

wpa-ssid youressid

wpa-psk 151790fab3bf3a1751a269618491b54984e192aa19319fc667397d45ec8dee5b

To have this take effect immediately:

service networking restart

For more information on configuring Wi-Fi, see Debian's guide here.

Debian 13 - Wi-Fi Access Point

hostapd needs to be installed if it is not already in order to manage the access point on the device:

apt-get update && apt-get install hostapd -y

| Note: | The install process will start an unconfigured hostapd process. This process must be killed and restarted before new hostapd.conf contents will take effect.

|

Edit /etc/hostapd/hostapd.conf to include the following lines:

interface=wlan0

ssid=YourWiFiName

wpa_passphrase=Somepassphrase

interface=wlan0

channel=7

driver=nl80211

logger_stdout=-1 # Print all module output to standard out

logger_stdout_level=2 # Print informational messages to standard out

wpa=2

wpa_key_mgmt=WPA-PSK

| Note: | Refer to the kernel's hostapd documentation for more wireless configuration options. |

To start the access point launch hostapd:

hostapd /etc/hostapd/hostapd.conf &

This will start up an access point that can be detected by Wi-Fi clients. A DHCP server will likely be desired to assign IP addresses. Refer to Debian's documentation for more details on DHCP configuration.

Debian 13 - Wi-Fi Concurrent Client / Access Point

The Wi-Fi device on this platform supports concurrent operation of client and access point (STA and AP). Please see the "Wi-Fi Client" section above first to connect the Wi-Fi module, in STA mode, to an external AP. This demo showcases the Wi-Fi module starting its own AP mode via hostapd with a simple static IP address while also being concurrently connected to a separate AP.

The hostapd utility is used to manage the access point mode. This is usually installed by default, but can separately be installed with:

apt-get update && apt-get install hostapd -y

| Note: | The install process may start an unconfigured 'hostapd' process. This process must be killed before moving forward. |

Modify the file /etc/hostapd/hostapd.conf to have the following lines:

ssid=YourWiFiName

wpa_passphrase=Somepassphrase

interface=p2p0

auth_algs=3

channel=<channel>

driver=nl80211

logger_stdout=-1

logger_stdout_level=2

wpa=2

wpa_key_mgmt=WPA-PSK

| Note: | The channel used for AP must match the channel the STA is using! Be sure to set 'channel=...' in the above file to a proper channel number. |

| Note: | Refer to the kernel's hostapd documentation for more wireless configuration options. |

In order for the concurrent modes to work, a separate virtual wireless device must first be created. Note that hostapd.conf above lists interface=p2p0, a virtual interface with this name must be created:

iw wlan0 interface add p2p0 type managed

The access point can then be started and tested by hand:

hostapd /etc/hostapd/hostapd.conf &

An IP address can be set to p2p0:

ifconfig p2p0 192.168.0.1

From this point, other Wi-Fi clients can connect to the SSID YourWiFiName with the WPA2 key Somepassphrase with a static IP in the range of 192.168.0.0/24, and will be able to access the platform at 192.168.0.1. More advanced configurations are also possible, including bridging, routing/NAT, or simply separate networks with the Wi-Fi module connecting to a network and hosting its own private network with DHCP.

Debian 13 - Installing New Software

Debian uses the Advanced Package Tool (APT) suite to manage installation of prebuilt applications. The APT tools require a network connection to the internet in order to automatically download and install new software. The update command will download a list of the current versions of available packages:

apt-get update

A common example is installing a simple web server like nginx. Find the package name first with search, and then install it:

root@host:~# apt-cache search nginx ... nginx - small, powerful, scalable web/proxy server nginx-common - small, powerful, scalable web/proxy server - common files nginx-core - nginx web/proxy server (standard version) nginx-dev - nginx web/proxy server - development headers nginx-doc - small, powerful, scalable web/proxy server - documentation nginx-extras - nginx web/proxy server (extended version) nginx-full - nginx web/proxy server (standard version with 3rd parties) nginx-light - nginx web/proxy server (basic version) nginx-confgen - nginx configuration file macro language and preprocessor ...

In this case, the wanted package will likely be the nginx package itself. Names of packages can be found on Debian's wiki pages or the Debian packages site.

With the package name apt-get install can be used to install the prebuilt packages.

apt-get install nginx

# More than one package can be installed at a time.

apt-get install nginx nano vim vbindiff

For more information on using the various APT tools, refer to Debian's APT documentation.

Debian 13 - Controlling GPIO

This distribution uses the gpiod (version 2.2.x) suite of tools and libraries for GPIO control.

In the 2.2.x releases, GPIO control revolves around GPIO line labels. Every GPIO present on the platform can be listed with gpioinfo:

root@host:~# gpioinfo

gpiochip0 - 32 lines:

line 0: unnamed input

line 1: unnamed input

line 2: unnamed output active-low consumer=red:status

...

gpiochip1 - 32 lines:

...

line 11: "USB_HUB_RESET#" output

...

line 19: "EN_MODBUS_24V" input

line 22: "EN_USB_5V" output

...

The first column, gpiochipX - YY lines lists the GPIO chip number and how many lines are connected to it. The second column, line xx:, lists the line number. The third column lists the name/label of that line. And the fourth column lists if the line is an input, output, polarity, and if it is actively being consumed.

GPIO pins can be set to an input state and their state read via gpioget:

root@host:~# gpioget "<line label>" "<line label>"=<state>

Where <line label> is replaced with a valid line label.

GPIO output states can be set with the gpioset tool. For example, to disable and then re-enable USB 5 V power (on compatible platforms

root@host:~# timeout 0.1 gpioset "EN_USB_5V"=0 root@host:~# timeout 0.1 gpioset "EN_USB_5V"=1

Note that "EN_USB_5V" may be different on some platforms. See the output of gpioinfo on a platform for the full list of GPIO pins, or look at the GPIO section for the list of line names. Additionally, timeout 0.1 is used as the 2.2.x version of gpiod will run in the foreground to consume the GPIO pin to ensure no other process can change its state.

See the gpiod 2.2.x documentation for more detail on the command line tools, as well as its various APIs.

Debian 13 - Setting up SSH

OpenSSH is installed in our Debian images, but by default OpenSSH does not permit logging in as the root user as a security measure. Even if logging in as root is enabled, a password must be set for the root account. Additionally, an SSH host key is required if one hasn't already been created (though this should automatically be created on the first boot).

It is generally discouraged to allow the root user to log in directly. Instead, a user account should be created, with a password set on it. No changes are needed to the OpenSSH configuration file to allow a non-root user to log in.

However, in order to login to a device as root via SSH, the following steps must occur:

sed --in-place 's/#PermitRootLogin prohibit-password/PermitRootLogin yes/' /etc/ssh/sshd_config

systemctl restart ssh.service

passwd root # Set any password

Debian 13 - Starting Automatically

A systemd service can be created to start up various applications. Create the file /etc/systemd/system/yourapp.service with the contents:

[Unit]

Description=Run an application on startup

# Uncomment the following line if networking is a dependency of the application being run

# After=network.target

[Service]

Type=simple

ExecStart=/usr/local/bin/your_app_or_script

[Install]

WantedBy=multi-user.target

The service can be started immediately and enableed on future boots with the following:

# Start the app on startup, but will not start it now

systemctl enable yourapp.service

# Start the app now, but doesn't change auto startup

systemctl start yourapp.service

See the systemd documentation for more information on how systemd services can be set up and configured.

Debian 13 - Cross Compiling

Debian provides cross toolchains within their distribution for different architectures.

For best portability, we recommend using a containerized environment like Docker to run a Debian 13 environment for toolchain access. This will allow a consistent build environment to run from almost any Linux system that can run Docker. Keep in mind that while docker does run under macOS and Windows, these are run under a case insensitive filesystem which will cause problems with complex builds like the Linux kernel so a Linux host is still recommended.

- Ubuntu/Debian:

sudo apt-get install docker.io -y

- Fedora

sudo dnf install docker -y

After installing docker on any distribution make sure your user is in the docker group:

# Add your user to the docker group. You may need to logout/log back in.

sudo usermod -aG docker $USER

Make sure you can run docker's hello world image as your user to verify it is working:

docker run hello-world

Now create a file Dockerfile:

sudo mkdir -p /opt/docker-toolchain/docker-debian-trixie-armhf

# Use any preferred editor, vim/emacs/nano/etc

sudo nano /opt/docker-toolchain/docker-debian-trixie-armhf/Dockerfile

# syntax = docker/dockerfile:1.2

FROM debian:trixie

RUN dpkg --add-architecture armhf

RUN apt-get update && apt-get install -y \

autogen \

automake \

bash \

bc \

bison \

build-essential \

bzip2 \

ca-certificates \

ccache \

chrpath \

cpio \

curl \

diffstat \

fakeroot \

file \

flex \

gawk \

gcc-arm-linux-gnueabihf \

git \

gzip \

kmod \

libgpiod-dev:armhf \

libncurses-dev \

libssl-dev \

libtool \

libyaml-dev \

locales \

lz4 \

lzop \

make \

pkg-config \

python3 \

python3-cbor \

python3-pexpect \

python3-pip \

qemu-user-static \

rsync \

runit \

socat \

srecord \

swig \

texinfo \

u-boot-tools \

zstd \

unzip \

vim \

wget \

xz-utils

# Provide a more friendly name

ENV debian_chroot debian_trixie

RUN echo "PS1='\${debian_chroot}\\[\033[01;32m\\]@\\H\[\\033[00m\\]:\\[\\033[01;34m\\]\\w\\[\\033[00m\\]\\$ '" >> /etc/bash.bashrc

# Set up locales

RUN sed -i -e 's/# en_US.UTF-8 UTF-8/en_US.UTF-8 UTF-8/' /etc/locale.gen && \

echo 'LANG="en_US.UTF-8"'>/etc/default/locale && \

dpkg-reconfigure --frontend=noninteractive locales && \

update-locale LANG=en_US.UTF-8

ENV LC_ALL en_US.UTF-8

ENV LANG en_US.UTF-8

ENV LANGUAGE en_US.UTF-8

Next make a shell script to enter into this docker container. Create /usr/local/bin/docker-debian-trixie:

# Use any preferred editor, vim/emacs/nano/etc

sudo nano /usr/local/bin/docker-debian-trixie

#!/bin/bash -e

# Enters a docker running Debian 13 Trixie

# Any arguments are run in the docker, or if no arguments it runs a shell

export TAG=debian-trixie-armdev

SCRIPTPATH=$(readlink -f "$0")

DOCKERPATH=/opt/docker-toolchain/docker-debian-trixie-armhf/

DOCKER_BUILDKIT=1 docker build --tag "$TAG" "$DOCKERPATH" --quiet

exec docker run --rm \

-it \

--volume "$(pwd)":/work \

--user $(id -u):$(id -g) \

-w /work \

-e HOME=/tmp \

"$TAG" \

$@;

Make this executable, and call it:

sudo chmod a+x /usr/local/bin/docker-debian-trixie

# dont run as root

docker-debian-trixie

The first time this runs it will download a base Debian image, and run the above apt-get commands which may take around 10 or so minutes depending on your internet connection and disk speed. After it has run once, it will stay cached and adds almost no overhead to run.

This Docker container can be thought of as a very low overhead virtual machine that only has access to the directory where it is run.

For example, to build a simple c project, create a ~/Desktop/hello-world/ directory:

mkdir -p ~/Desktop/hello-world/

In ~/Desktop/hello-world/hello.c:

#include <stdio.h>

int main() {

printf("Hello world!\n");

return 0;

}

We can now use the docker in that directory to use Debian's cross compiler to create a binary that targets armhf:

user@hostname:~$ cd ~/Desktop/hello-world/ user@hostname:~/Desktop/hello-world$ docker-debian-trixie sha256:a92e70c3d7346654b34c0442da20ae634901fd25d1a89dd26517e7d1c1d00c47 debian_trixie@a8ddfa54989f:/work$ ls hello.c debian_trixie@a8ddfa54989f:/work$ arm-linux-gnueabihf-gcc hello.c -o hello debian_trixie@a8ddfa54989f:/work$ arm-linux-gnueabihf-strip hello debian_trixie@a8ddfa54989f:/work$ file hello hello: ELF 32-bit LSB pie executable, ARM, EABI5 version 1 (SYSV), dynamically linked, interpreter /lib/ld-linux-armhf.so.3, BuildID[sha1]=ffda981721a1531418ed1da27238707851ae0126, for GNU/Linux 3.2.0, stripped

Debian 12 - Bookworm

Debian 12 - Getting Started

This Debian release is available in 2 flavors with various packages. See our Debian releases in the Software Images section for links to the latest images available.

| Image | Description |

|---|---|

| Headless |

|

| Minimal |

|

The default login is root with no password.

Debian 12 - Networking

The network in Debian is configured with /etc/network/interfaces. For complete documentation, see Debian's documentation here

Some common examples are shown below. On this release network interfaces follow the predictible network interface names. Run ip addr show to get a list of the network interfaces.

Most commonly:

- end0 - Ethernet device 0 (CPU Ethernet)

- enp1s0 - Ethernet PCIe port 1 slot 0 Ethernet

- usb<mac> - USB Ethernet

- wlan0 - Wi-Fi

DHCP on end0. Create the file /etc/network/interfaces.d/end0 with the contents:

allow-hotplug end0 iface end0 inet dhcp

Static IP on end0. Create the file /etc/network/interfaces.d/end0 with the contents:

allow-hotplug end0

iface end0 inet static

address 192.0.2.7/24

gateway 192.0.2.254

These will take effect on the next boot, or by restarting the networking service:

service networking restart

Debian 12 - Wi-Fi Client

Wireless interfaces are also managed with configuration files in /etc/network/interfaces.d/. For example, to connect as a client to a WPA network with DHCP. Note some or all of this software may already be installed on the target.

Install wpa_supplicant:

apt-get update && apt-get install wpasupplicant -y

Run:

wpa_passphrase youressid yourpassword

This command will output information similar to:

network={

ssid="youressid"

#psk="yourpassword"

psk=151790fab3bf3a1751a269618491b54984e192aa19319fc667397d45ec8dee5b

}

Use the hashed PSK in the specific network interfaces file for added security. Create the file /etc/network/interfaces.d/wlan0 with the contents:

allow-hotplug wlan0

iface wlan0 inet dhcp

wpa-ssid youressid

wpa-psk 151790fab3bf3a1751a269618491b54984e192aa19319fc667397d45ec8dee5b

To have this take effect immediately:

service networking restart

For more information on configuring Wi-Fi, see Debian's guide here.

Debian 12 - Wi-Fi Access Point

hostapd needs to be installed if it is not already in order to manage the access point on the device:

apt-get update && apt-get install hostapd -y

| Note: | The install process will start an unconfigured hostapd process. This process must be killed and restarted before new hostapd.conf contents will take effect.

|

Edit /etc/hostapd/hostapd.conf to include the following lines:

interface=wlan0

ssid=YourWiFiName

wpa_passphrase=Somepassphrase

interface=wlan0

channel=7

driver=nl80211

logger_stdout=-1 # Print all module output to standard out

logger_stdout_level=2 # Print informational messages to standard out

wpa=2

wpa_key_mgmt=WPA-PSK

| Note: | Refer to the kernel's hostapd documentation for more wireless configuration options. |

To start the access point launch hostapd:

hostapd /etc/hostapd/hostapd.conf &

This will start up an access point that can be detected by Wi-Fi clients. A DHCP server will likely be desired to assign IP addresses. Refer to Debian's documentation for more details on DHCP configuration.

Debian 12 - Wi-Fi Concurrent Client / Access Point

The Wi-Fi device on this platform supports concurrent operation of client and access point (STA and AP). Please see the "Wi-Fi Client" section above first to connect the Wi-Fi module, in STA mode, to an external AP. This demo showcases the Wi-Fi module starting its own AP mode via hostapd with a simple static IP address while also being concurrently connected to a separate AP.

The hostapd utility is used to manage the access point mode. This is usually installed by default, but can separately be installed with:

apt-get update && apt-get install hostapd -y

| Note: | The install process may start an unconfigured 'hostapd' process. This process must be killed before moving forward. |

Modify the file /etc/hostapd/hostapd.conf to have the following lines:

ssid=YourWiFiName

wpa_passphrase=Somepassphrase

interface=p2p0

auth_algs=3

channel=<channel>

driver=nl80211

logger_stdout=-1

logger_stdout_level=2

wpa=2

wpa_key_mgmt=WPA-PSK

| Note: | The channel used for AP must match the channel the STA is using! Be sure to set 'channel=...' in the above file to a proper channel number. |

| Note: | Refer to the kernel's hostapd documentation for more wireless configuration options. |

In order for the concurrent modes to work, a separate virtual wireless device must first be created. Note that hostapd.conf above lists interface=p2p0, a virtual interface with this name must be created:

iw wlan0 interface add p2p0 type managed

The access point can then be started and tested by hand:

hostapd /etc/hostapd/hostapd.conf &

An IP address can be set to p2p0:

ifconfig p2p0 192.168.0.1

From this point, other Wi-Fi clients can connect to the SSID YourWiFiName with the WPA2 key Somepassphrase with a static IP in the range of 192.168.0.0/24, and will be able to access the platform at 192.168.0.1. More advanced configurations are also possible, including bridging, routing/NAT, or simply separate networks with the Wi-Fi module connecting to a network and hosting its own private network with DHCP.

Debian 12 - Installing New Software

Debian uses the Advanced Package Tool (APT) suite to manage installation of prebuilt applications. The APT tools require a network connection to the internet in order to automatically download and install new software. The update command will download a list of the current versions of available packages:

apt-get update

A common example is installing a simple web server like nginx. Find the package name first with search, and then install it:

root@host:~# apt-cache search nginx ... nginx - small, powerful, scalable web/proxy server nginx-common - small, powerful, scalable web/proxy server - common files nginx-core - nginx web/proxy server (standard version) nginx-dev - nginx web/proxy server - development headers nginx-doc - small, powerful, scalable web/proxy server - documentation nginx-extras - nginx web/proxy server (extended version) nginx-full - nginx web/proxy server (standard version with 3rd parties) nginx-light - nginx web/proxy server (basic version) nginx-confgen - nginx configuration file macro language and preprocessor ...

In this case, the wanted package will likely be the nginx package itself. Names of packages can be found on Debian's wiki pages or the Debian packages site.

With the package name apt-get install can be used to install the prebuilt packages.

apt-get install nginx

# More than one package can be installed at a time.

apt-get install nginx nano vim vbindiff

For more information on using the various APT tools, refer to Debian's APT documentation.

Debian 12 - Setting up SSH

OpenSSH is installed in our Debian images, but by default OpenSSH does not permit logging in as the root user as a security measure. Even if logging in as root is enabled, a password must be set for the root account. Additionally, an SSH host key is required if one hasn't already been created (though this should automatically be created on the first boot).

It is generally discouraged to allow the root user to log in directly. Instead, a user account should be created, with a password set on it. No changes are needed to the OpenSSH configuration file to allow a non-root user to log in.

However, in order to login to a device as root via SSH, the following steps must occur:

sed --in-place 's/#PermitRootLogin prohibit-password/PermitRootLogin yes/' /etc/ssh/sshd_config

systemctl restart ssh.service

passwd root # Set any password

Debian 12 - Starting Automatically

A systemd service can be created to start up various applications. Create the file /etc/systemd/system/yourapp.service with the contents:

[Unit]

Description=Run an application on startup

# Uncomment the following line if networking is a dependency of the application being run

# After=network.target

[Service]

Type=simple

ExecStart=/usr/local/bin/your_app_or_script

[Install]

WantedBy=multi-user.target

The service can be started immediately and enableed on future boots with the following:

# Start the app on startup, but will not start it now

systemctl enable yourapp.service

# Start the app now, but doesn't change auto startup

systemctl start yourapp.service

See the systemd documentation for more information on how systemd services can be set up and configured.

Debian 12 - Cross Compiling

Debian provides cross toolchains within their distribution for different architectures.

For best portability, we recommend using a containerized environment like Docker to run a Debian 12 environment for toolchain access. This will allow a consistent build environment to run from almost any Linux system that can run Docker. Keep in mind that while docker does run under macOS and Windows, these are run under a case insensitive filesystem which will cause problems with complex builds like the Linux kernel so a Linux host is still recommended.

- Ubuntu/Debian:

sudo apt-get install docker.io -y

- Fedora

sudo dnf install docker -y

After installing docker on any distribution make sure your user is in the docker group:

# Add your user to the docker group. You may need to logout/log back in.

sudo usermod -aG docker $USER

Make sure you can run docker's hello world image as your user to verify it is working:

docker run hello-world

Now create a file Dockerfile:

sudo mkdir -p /opt/docker-toolchain/docker-debian-bookworm-armhf

# Use any preferred editor, vim/emacs/nano/etc

sudo nano /opt/docker-toolchain/docker-debian-bookworm-armhf/Dockerfile

# syntax = docker/dockerfile:1.2

FROM debian:bookworm

RUN dpkg --add-architecture armhf

RUN apt-get update && apt-get install -y \

autogen \

automake \

bash \

bc \

bison \

build-essential \

bzip2 \

ca-certificates \

ccache \

chrpath \

cpio \

curl \

diffstat \

fakeroot \

file \

flex \

gawk \

gcc-arm-linux-gnueabihf \

git \

gzip \

kmod \

libgpiod-dev:armhf \

libncursesw5-dev \

libssl-dev \

libtool \

libyaml-dev \

locales \

lz4 \

lzop \

make \

multistrap \

ncurses-dev \

pkg-config \

python3 \

python3-cbor \

python3-pexpect \

python3-pip \

qemu-user-static \

rsync \

runit \

socat \

srecord \

swig \

texinfo \

u-boot-tools \

zstd \

unzip \

vim \

wget \

xz-utils

# Provide a more friendly name

ENV debian_chroot debian_bookworm

RUN echo "PS1='\${debian_chroot}\\[\033[01;32m\\]@\\H\[\\033[00m\\]:\\[\\033[01;34m\\]\\w\\[\\033[00m\\]\\$ '" >> /etc/bash.bashrc

# Set up locales

RUN sed -i -e 's/# en_US.UTF-8 UTF-8/en_US.UTF-8 UTF-8/' /etc/locale.gen && \

echo 'LANG="en_US.UTF-8"'>/etc/default/locale && \

dpkg-reconfigure --frontend=noninteractive locales && \

update-locale LANG=en_US.UTF-8

ENV LC_ALL en_US.UTF-8

ENV LANG en_US.UTF-8

ENV LANGUAGE en_US.UTF-8

Next make a shell script to enter into this docker container. Create /usr/local/bin/docker-debian-bookworm:

# Use any preferred editor, vim/emacs/nano/etc

sudo nano /usr/local/bin/docker-debian-bookworm

#!/bin/bash -e

# Enters a docker running Debian 12 Bookworm

# Any arguments are run in the docker, or if no arguments it runs a shell

export TAG=debian-bookworm-armdev

SCRIPTPATH=$(readlink -f "$0")

DOCKERPATH=/opt/docker-toolchain/docker-debian-bookworm-armhf/

DOCKER_BUILDKIT=1 docker build --tag "$TAG" "$DOCKERPATH" --quiet

exec docker run --rm \

-it \

--volume "$(pwd)":/work \

--user $(id -u):$(id -g) \

-w /work \

-e HOME=/tmp \

"$TAG" \

$@;

Make this executable, and call it:

sudo chmod a+x /usr/local/bin/docker-debian-bookworm

# dont run as root

docker-debian-bookworm

The first time this runs it will download a base Debian image, and run the above apt-get commands which may take around 10 or so minutes depending on your internet connection and disk speed. After it has run once, it will stay cached and adds almost no overhead to run.

This docker can be thought of as a very low overhead virtual machine that only has access to the directory where it is run.

For example, to build a simple c project, create a ~/Desktop/hello-world directory:

mkdir -p ~/Desktop/hello-world/

In ~/Desktop/hello-world/hello.c:

#include <stdio.h>

int main() {

printf("Hello world!\n");

return 0;

}

We can now use the docker in that directory to use Debian's cross compiler to create a binary that targets armhf: