TS-9370

This product is under engineering sampling, and is still under development.

This product supports applying firmware updates to the FPGA and onboard microcontroller (Wizard) so many features will be provided as updates in the field as they are completed.

| Feature | Status | Notes |

|---|---|---|

| Ethernet | Working | Tested iperf on both ports to validate 1Gb/s. Tested nfs booting, no issues seen with Ethernet traffic. Some features like PTP are currently not tested. |

| eMMC | Working | Preliminarily Tested. The bootloader is loaded from mmc0 boot partition 0. Tested booting to Linux and reading/writing. |

| USB Host Ports | Working | Tested USB drives enumerate and read/write data. |

| RTC | Working | Verified this RTC from the wizard holds and retains time. |

| FPGA PWM controller | Working | Preliminarily Tested |

| Serial | Working | Tested all TTL, RS-485, RS-232 ports. Verified CPU's RTS ports toggle automatically supporting TX-EN. Tested picocom to work on all ports to send/receive data. Testing with linux-serial-test shows a 100ms rx delay is required when sending at full speed. Some UART test applications are showing dropped characters immediately on open which is being investigated. Does not appear to drop data after the port is opened and some initial data is sent. |

| CAN | Working | Tested against CAN devices. Controller and installed transceiver support CAN-FD, but FD devices have not yet been tested. |

| GPIO | Working | Tested CPU IO and FPGA controllers to be working, and support interrupts on rising/falling/both edges. |

| Nimbelink | Working | Tested UARTs. Examples yet to be provided on suggested control of the other I/O for bringing up specific modems. |

| Terminal Block Circuit Breaker | Working | Preliminarily tested, requires FPGA v0.2.6 or later. |

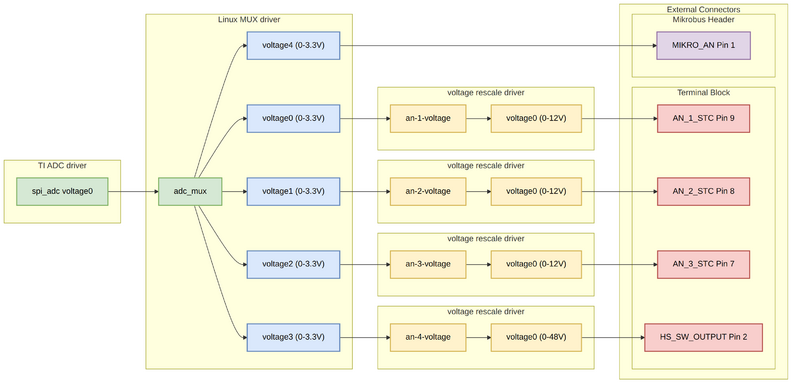

| 4-20mA/0-13.2V ADC | Completed | Working with FPGA v0.2.8 and Kernels after 07/16/2025 |

| SPI | Working | Preliminarily tested with default spidev + loopbacks and an oscilloscope. |

| FPGA XBAR | Working | Tested in FPGA v0.2.7 and later. |

| i.MX93 NPU | Working | Tested with 6.6.52 kernel. See NPU documentation section for script to install software support. |

| DisplayPort | Working | Working as of P4 |

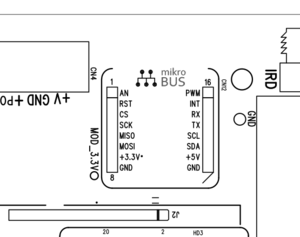

| Mikrobus | Working | All Mikrobus Interfaces, SPI, I2C, PWM, INT, RST, TXD/RXD, and MIKRO_AN have had preliminary testing. |

| Accelerometer-Gyro | Working | Supports individual samples with iio_info. |

| Magnetometer | Working | Supports individual samples with iio_info. |

| WIFI | Working | Tested client with wpa_supplicant and ap with hostapd |

| Audio Codec | Working | Tested mono in and mono out with aplay/arecord. Works at 48KHz, requires configuration change for 44.1KHz |

| Bluetooth | Working | Tested with bluetoothctl scan |

| i.MX93 low power sleep | Working | Suspend to ram works, tested with wakeup from tty |

| i.MX93 M33 | Working | This is the ARM Cortex-M33 microcontroller built into the i.MX93, allowing users to run some code in an RTOS like Zephyr or FreeRTOS. Tested with sysfs remoteproc interface |

| Image Replicator | Working | This is the USB tool to rewrite the image on production units. |

| microSD | Not working | Not working on the TS-9370 P4, will be fixed on the next revision. |

| TS-SILO Supercap Backup | TODO | The TS-SILO will provide backup power after power has been lost, which provides time to properly shutdown and unmount drives after power has been lost. This has been preliminarily tested in the hardware and will be provided as a future Wizard update, and Linux driver update. |

| Wizard low power sleep | TODO | This feature will allow powering off the i.MX93, FPGA, and most ICs, but allow waking on RTC alarm, push button, and planned on a future PCB revision is movement from the accelerometer/gyro. |

| i.MX93 Low drive mode | TODO | This lower performance / operating mode that allows lower runtime power. This requires further changes in the FPGA/linux to implement. |

| Open Source FPGA | TODO | The FPGA is planned to be open sourced, and will be after some additional features are stabilized. |

| |

| Product Page | |

| Documentation | |

|---|---|

| Schematic | |

| FTP Path | |

| Processor | |

| NXP i.MX9352 | |

| 1.7 GHz Arm® Cortex®-A55/M33 | |

| i.MX93 Product Page | |

| CPU Documentation |

Overview

The TS-9370 is a single board computer providing an i.MX93 based SOC, an Intel MAX 10 FPGA, an onboard eMMC, MicroSD, WIFI, BT, an amplified speaker output, and an assortment of ADC, and wide range IO.

Getting Started

A Linux workstation is recommended and assumed for development using this documentation. For users in Windows or OSX, we recommend virtualizing Linux using VMWare or similar to make the full power of Linux available. The developer should be comfortable with Linux to work with embedded Linux on the target platform. Most of our platforms run Debian, which is recommended for ease of use if there is no personal distribution preference.

The main reasons that Linux is useful are:

- Linux filesystems on the microSD card can be accessed on the PC.

- More ARM cross-compilers are available.

- If recovery is needed, a bootable medium can be written.

- A network filesystem can be served.

- Builds such as Linux kernel, Buildroot, Yocto, and distro-seed will not work from WSL1/2 on a case-insensitive filesystem.

| WARNING: | Be sure to take appropriate Electrostatic Discharge (ESD) precautions. Disconnect the power source before moving, cabling, or performing setup procedures. Inappropriate handling may cause damage to the board. |

U-Boot

U-Boot is a bootloader and comes preinstalled on this board. The U-Boot bootloader is loaded in the eMMC hardware boot partitions in /dev/mmcblk0boot0. U-Boot sets up the hardware and then loads the OS from the available storage devices. U-Boot allows booting images from the microSD, eMMC, NFS, or USB. Most users will not need to customize u-boot further, and can proceed to the #Debian, #Ubuntu, #Yocto, or #Buildroot sections for information on application development.

U-Boot Standard Boot

This platform uses u-boot's "Standard Boot" as the method to search available storage media for a bootable operating system.

By default the board will attempt booting to these devices:

| boot_target | Description |

|---|---|

| usb | U-boot will probe for any available USB Storage media |

| mmc1 | microSD |

| mmc0 | Onboard eMMC flash |

| pxe | Network boot |

The order, and the enabled boot targets can be customized by changing the variable:

# Boot to eMMC only:

setenv boot_targets mmc0

# Boot to USB, then eMMC:

setenv boot_targets usb mmc0

# Default targets

setenv boot_targets usb mmc1 mmc0 pxe

While searching each media, u-boot searches for valid boot methods on each device.

| bootmeths | Description |

|---|---|

| script | Legacy distro-boot scripts. Looks for /boot/boot.scr, /boot/boot.scr.uimg, and executes those |

| extlinux | Looks for extlinux/extlinux.conf. See the syslinux project for more details. |

| efi | Looks for an EFI boot partition, and executes the EFI payload such as grub, or the Linux kernel. |

| pxe | For PXE boot only, checks for valid DHCP describing boot. |

The order, and the enabled boot methods can be customized by changing the variable:

# Only boot extlinux:

setenv bootmeths extlinux

# Try script, then EFI

setenv bootmeths script efi

# Default bootmeths

setenv bootmeths script extlinux efi pxe

On our factory preprogrammed images the typical boot skips USB, mmc1, and boots to a script on eMMC.

U-Boot Environment

The U-Boot environment is stored in the on-board eMMC flash in the /dev/mmcblk0boot0 partition.

It can be accessed from the u-boot shell:

# Print all environment variables

env print -a

# Sets the variable bootdelay to 5 seconds

env set bootdelay 5

# Variables can also contain commands

env set hellocmd 'led green:indicator off; echo Hello world; led green:indicator on;'

# Execute commands saved in a variable

env run hellocmd

# Commit env changes to the emmc

# Otherwise changes are lost

env save

# Remove a variable

env delete hellocmd

# Restore env to default

env default -a

# Save default env or it will revert next reset

env save

Booting From NFS

U-Boot Development

The TS-9370 u-boot is built using Yocto, even if booting other Distributions such as Debian/Ubuntu. See the Yocto Walnascar build instructions for getting started.

Once the yocto environment is set up, build a u-boot with:

bitbake bitbake imx-boot u-boot-imx

In your Yocto build directory this will generate a tmp/deploy/images/ts9370/imx-boot-ts9370-sd.bin-flash_singleboot file. This should be written to mmcblk0boot0 at offset 0.

Install the dependencies on your Linux Workstation:

- wizusb

- access to Wizard registers over USB

- NXP mfgtools

- uuu tool for booting/flashing i.MX93 over USB

Connect a TC2030-USB cable to CN66. This connector is on the corner near the type A USB. Keep in mind this is run in parallel with the top port of J2 which should not have anything connected while CN66 is connected.

To load a singleboot image on the board, run:

# Switch boot to USB Serial Downloader

wizusb 17 0x1

# Reset the board, so it comes up in the new strapping

wizusb 8 0x1

# Boot + Program u-boot over USB:

uuu -b emmc /path/to/singleboot

# Switch boot to USDHC1 8-bit eMMC

wizusb 17 0x2

# Reset the board, so it comes up in the new strapping

wizusb 8 0x1

Debian

Debian 13 - Trixie

Debian 13 - Getting Started

This Debian release is available in 3 flavors with various packages.

| Image | Estimated Size | Description |

|---|---|---|

| tsimx9-debian-13-trixie-x11-latest.tar.xz | 1677 MiB |

|

| tsimx9-debian-13-trixie-headless-latest.tar.xz | 1369 MiB |

|

| tsimx9-debian-13-trixie-minimal-latest.tar.xz | 792 MiB |

|

The default login is root with no password.

To write this to an SD card, first partition the SD card to have one large ext4 partition. Once it is formatted, extract this tar with:

# Assuming your SD card is /dev/sdc with one partition

mkfs.ext4 /dev/sdc1

mkdir /mnt/sd/

sudo mount /dev/sdc1 /mnt/sd/

sudo tar --numeric-owner -xJf tsimx9-debian-13-trixie-x11-latest.tar.xz -C /mnt/sd

sudo umount /mnt/sd

sync

To rewrite the eMMC, boot to the SD card. You cannot rewrite the emmc while it is mounted elsewhere, or used to currently boot the system. Once booted to the SD, run:

mkfs.ext3 /dev/mmcblk2p1

mkdir /mnt/emmc

mount /dev/mmcblk2p1 /mnt/emmc

wget -qO- https://files.embeddedts.com/ts-arm-sbc/ts-9370-linux/distributions/debian/ tsimx9-debian-13-trixie-x11-latest.tar.xz | tar --numeric-owner -xJ -C /mnt/emmc/

umount /mnt/emmc

sync

Debian 13 - Networking

The network in Debian is configured with /etc/network/interfaces. For complete documentation, see Debian's documentation here

Some common examples are shown below. On this release network interfaces follow the predictible network interface names. Run ip addr show to get a list of the network interfaces.

Most commonly:

- end0 - Ethernet device 0 (CPU Ethernet)

- enp1s0 - Ethernet PCIe port 1 slot 0 Ethernet

- usb<mac> - USB Ethernet

- wlan0 - Wi-Fi

DHCP on end0. Create the file /etc/network/interfaces.d/end0 with the contents:

allow-hotplug end0 iface end0 inet dhcp

Static IP on end0. Create the file /etc/network/interfaces.d/end0 with the contents:

allow-hotplug end0

iface end0 inet static

address 192.0.2.7/24

gateway 192.0.2.254

These will take effect on the next boot, or by restarting the networking service:

service networking restart

Debian 13 - Wi-Fi Client

Wireless interfaces are also managed with configuration files in /etc/network/interfaces.d/. For example, to connect as a client to a WPA network with DHCP. Note some or all of this software may already be installed on the target.

Install wpa_supplicant:

apt-get update && apt-get install wpasupplicant -y

Run:

wpa_passphrase youressid yourpassword

This command will output information similar to:

network={

ssid="youressid"

#psk="yourpassword"

psk=151790fab3bf3a1751a269618491b54984e192aa19319fc667397d45ec8dee5b

}

Use the hashed PSK in the specific network interfaces file for added security. Create the file /etc/network/interfaces.d/wlan0 with the contents:

allow-hotplug wlan0

iface wlan0 inet dhcp

wpa-ssid youressid

wpa-psk 151790fab3bf3a1751a269618491b54984e192aa19319fc667397d45ec8dee5b

To have this take effect immediately:

service networking restart

For more information on configuring Wi-Fi, see Debian's guide here.

Debian 13 - Wi-Fi Access Point

hostapd needs to be installed if it is not already in order to manage the access point on the device:

apt-get update && apt-get install hostapd -y

| Note: | The install process will start an unconfigured hostapd process. This process must be killed and restarted before new hostapd.conf contents will take effect.

|

Edit /etc/hostapd/hostapd.conf to include the following lines:

interface=wlan0

ssid=YourWiFiName

wpa_passphrase=Somepassphrase

interface=wlan0

channel=7

driver=nl80211

logger_stdout=-1 # Print all module output to standard out

logger_stdout_level=2 # Print informational messages to standard out

wpa=2

wpa_key_mgmt=WPA-PSK

| Note: | Refer to the kernel's hostapd documentation for more wireless configuration options. |

To start the access point launch hostapd:

hostapd /etc/hostapd/hostapd.conf &

This will start up an access point that can be detected by Wi-Fi clients. A DHCP server will likely be desired to assign IP addresses. Refer to Debian's documentation for more details on DHCP configuration.

Debian 13 - Installing New Software

Debian uses the Advanced Package Tool (APT) suite to manage installation of prebuilt applications. The APT tools require a network connection to the internet in order to automatically download and install new software. The update command will download a list of the current versions of available packages:

apt-get update

A common example is installing a simple web server like nginx. Find the package name first with search, and then install it:

root@host:~# apt-cache search nginx ... nginx - small, powerful, scalable web/proxy server nginx-common - small, powerful, scalable web/proxy server - common files nginx-core - nginx web/proxy server (standard version) nginx-dev - nginx web/proxy server - development headers nginx-doc - small, powerful, scalable web/proxy server - documentation nginx-extras - nginx web/proxy server (extended version) nginx-full - nginx web/proxy server (standard version with 3rd parties) nginx-light - nginx web/proxy server (basic version) nginx-confgen - nginx configuration file macro language and preprocessor ...

In this case, the wanted package will likely be the nginx package itself. Names of packages can be found on Debian's wiki pages or the Debian packages site.

With the package name apt-get install can be used to install the prebuilt packages.

apt-get install nginx

# More than one package can be installed at a time.

apt-get install nginx nano vim vbindiff

For more information on using the various APT tools, refer to Debian's APT documentation.

Debian 13 - Setting up SSH

OpenSSH is installed in our Debian images, but by default OpenSSH does not permit logging in as the root user as a security measure. Even if logging in as root is enabled, a password must be set for the root account. Additionally, an SSH host key is required if one hasn't already been created (though this should automatically be created on the first boot).

It is generally discouraged to allow the root user to log in directly. Instead, a user account should be created, with a password set on it. No changes are needed to the OpenSSH configuration file to allow a non-root user to log in.

However, in order to login to a device as root via SSH, the following steps must occur:

sed --in-place 's/#PermitRootLogin prohibit-password/PermitRootLogin yes/' /etc/ssh/sshd_config

systemctl restart ssh.service

passwd root # Set any password

Debian 13 - Starting Automatically

A systemd service can be created to start up various applications. Create the file /etc/systemd/system/yourapp.service with the contents:

[Unit]

Description=Run an application on startup

# Uncomment the following line if networking is a dependency of the application being run

# After=network.target

[Service]

Type=simple

ExecStart=/usr/local/bin/your_app_or_script

[Install]

WantedBy=multi-user.target

The service can be started immediately and enableed on future boots with the following:

# Start the app on startup, but will not start it now

systemctl enable yourapp.service

# Start the app now, but doesn't change auto startup

systemctl start yourapp.service

See the systemd documentation for more information on how systemd services can be set up and configured.

Debian 13 - Cross Compiling

For building kernels targeting the Debian images we recommend using cqfd. This allows building a compatible kernel using identical tools from any build host.

To build a kernel for the embeddedTS i.MX93 based platforms:

- Make sure docker is installed, and can run hello world:

- docker run hello-world

- Make sure cqfd is installed:

# Install cqfd-linux-lts builds scripts

git clone https://github.com/embeddedTS/cqfd-linux-lts

cd cqfd-linux-lts

# Clone the Linux kernel

git clone https://github.com/embeddedTS/linux-tsimx.git -b lf-6.12.y linux

# Build the kernel:

./build_tsimx93_tar.sh

This will set up the container including Debian's cross compilers, and any dependencies needed to build the kernel. This runs once on initial setup, and the only when the Dockerfile is modified. Next, it builds the defconfig, compiles the kernel, and assembles a tar of the build objects for that image. After it completes, it will print out the path to the tar file.

At this point, the tarball can be unpacked to a bootable media for the device. This can be done from a booted device, or by mounting removable media from a host Linux workstation. For example, if the root folder of the target filesystem to be updated is mounted to /mnt/, the following can be used to unpack the above tarball:

# Ensure the target filesystem is mounted to /mnt first!

# Extract kernel tarball to target filesystem,

tar xhf linux-*.tar.gz -C /mnt

| Note: | The tar h argument to tar is necessary on recent distributions that merge /usr/. Not using it will render the system unbootable. |

Debian 13 - Compile the aarch64 Kernel

For building kernels targeting the Debian images we recommend using cqfd. This allows building a compatible kernel using identical tools from any build host.

To build a kernel for the embeddedTS i.MX93 based platforms:

- Make sure docker is installed, and can run hello world:

- docker run hello-world

- Make sure cqfd is installed:

# Install cqfd-linux-lts builds scripts

git clone https://github.com/embeddedTS/cqfd-linux-lts

cd cqfd-linux-lts

# Clone the Linux kernel

git clone https://github.com/embeddedTS/linux-tsimx.git -b lf-6.12.y linux

# Build the kernel:

./build_tsimx93_tar.sh

This will set up the container including Debian's cross compilers, and any dependencies needed to build the kernel. This runs once on initial setup, and the only when the Dockerfile is modified. Next, it builds the defconfig, compiles the kernel, and assembles a tar of the build objects for that image. After it completes, it will print out the path to the tar file.

At this point, the tarball can be unpacked to a bootable media for the device. This can be done from a booted device, or by mounting removable media from a host Linux workstation. For example, if the root folder of the target filesystem to be updated is mounted to /mnt/, the following can be used to unpack the above tarball:

# Ensure the target filesystem is mounted to /mnt first!

# Extract kernel tarball to target filesystem,

tar xhf linux-*.tar.gz -C /mnt

| Note: | The tar h argument to tar is necessary on recent distributions that merge /usr/. Not using it will render the system unbootable. |

Debian 12 - Bookworm

Debian 12 - Getting Started

This Debian release is available in 3 flavors with various packages.

| Image | Estimated Size | Description |

|---|---|---|

| tsimx9-debian-12-bookworm-x11-latest.tar.xz | 1233 MiB |

|

| tsimx9-debian-12-bookworm-headless-latest.tar.xz | 961 MiB |

|

| tsimx9-debian-12-bookworm-minimal-latest.tar.xz | 379 MiB |

|

The default login is root with no password.

To write this to an SD card, first partition the SD card to have one large ext4 partition. Once it is formatted, extract this tar with:

# Assuming your SD card is /dev/sdc with one partition

mkfs.ext4 /dev/sdc1

mkdir /mnt/sd/

sudo mount /dev/sdc1 /mnt/sd/

sudo tar --numeric-owner -xJf tsimx9-debian-12-bookworm-x11-latest.tar.xz -C /mnt/sd

sudo umount /mnt/sd

sync

To rewrite the eMMC, boot to the SD card. You cannot rewrite the emmc while it is mounted elsewhere, or used to currently boot the system. Once booted to the SD, run:

mkfs.ext3 /dev/mmcblk2p1

mkdir /mnt/emmc

mount /dev/mmcblk2p1 /mnt/emmc

wget -qO- https://files.embeddedts.com/ts-arm-sbc/ts-9370-linux/distributions/debian/ tsimx9-debian-12-bookworm-x11-latest.tar.xz | tar --numeric-owner -xJ -C /mnt/emmc/

umount /mnt/emmc

sync

Debian 12 - Networking

The network in Debian is configured with /etc/network/interfaces. For complete documentation, see Debian's documentation here

Some common examples are shown below. On this release network interfaces follow the predictible network interface names. Run ip addr show to get a list of the network interfaces.

Most commonly:

- end0 - Ethernet device 0 (CPU Ethernet)

- enp1s0 - Ethernet PCIe port 1 slot 0 Ethernet

- usb<mac> - USB Ethernet

- wlan0 - Wi-Fi

DHCP on end0. Create the file /etc/network/interfaces.d/end0 with the contents:

allow-hotplug end0 iface end0 inet dhcp

Static IP on end0. Create the file /etc/network/interfaces.d/end0 with the contents:

allow-hotplug end0

iface end0 inet static

address 192.0.2.7/24

gateway 192.0.2.254

These will take effect on the next boot, or by restarting the networking service:

service networking restart

Debian 12 - Wi-Fi Client

Wireless interfaces are also managed with configuration files in /etc/network/interfaces.d/. For example, to connect as a client to a WPA network with DHCP. Note some or all of this software may already be installed on the target.

Install wpa_supplicant:

apt-get update && apt-get install wpasupplicant -y

Run:

wpa_passphrase youressid yourpassword

This command will output information similar to:

network={

ssid="youressid"

#psk="yourpassword"

psk=151790fab3bf3a1751a269618491b54984e192aa19319fc667397d45ec8dee5b

}

Use the hashed PSK in the specific network interfaces file for added security. Create the file /etc/network/interfaces.d/wlan0 with the contents:

allow-hotplug wlan0

iface wlan0 inet dhcp

wpa-ssid youressid

wpa-psk 151790fab3bf3a1751a269618491b54984e192aa19319fc667397d45ec8dee5b

To have this take effect immediately:

service networking restart

For more information on configuring Wi-Fi, see Debian's guide here.

Debian 12 - Wi-Fi Access Point

hostapd needs to be installed if it is not already in order to manage the access point on the device:

apt-get update && apt-get install hostapd -y

| Note: | The install process will start an unconfigured hostapd process. This process must be killed and restarted before new hostapd.conf contents will take effect.

|

Edit /etc/hostapd/hostapd.conf to include the following lines:

interface=wlan0

ssid=YourWiFiName

wpa_passphrase=Somepassphrase

interface=wlan0

channel=7

driver=nl80211

logger_stdout=-1 # Print all module output to standard out

logger_stdout_level=2 # Print informational messages to standard out

wpa=2

wpa_key_mgmt=WPA-PSK

| Note: | Refer to the kernel's hostapd documentation for more wireless configuration options. |

To start the access point launch hostapd:

hostapd /etc/hostapd/hostapd.conf &

This will start up an access point that can be detected by Wi-Fi clients. A DHCP server will likely be desired to assign IP addresses. Refer to Debian's documentation for more details on DHCP configuration.

Debian 12 - Installing New Software

Debian uses the Advanced Package Tool (APT) suite to manage installation of prebuilt applications. The APT tools require a network connection to the internet in order to automatically download and install new software. The update command will download a list of the current versions of available packages:

apt-get update

A common example is installing a simple web server like nginx. Find the package name first with search, and then install it:

root@host:~# apt-cache search nginx ... nginx - small, powerful, scalable web/proxy server nginx-common - small, powerful, scalable web/proxy server - common files nginx-core - nginx web/proxy server (standard version) nginx-dev - nginx web/proxy server - development headers nginx-doc - small, powerful, scalable web/proxy server - documentation nginx-extras - nginx web/proxy server (extended version) nginx-full - nginx web/proxy server (standard version with 3rd parties) nginx-light - nginx web/proxy server (basic version) nginx-confgen - nginx configuration file macro language and preprocessor ...

In this case, the wanted package will likely be the nginx package itself. Names of packages can be found on Debian's wiki pages or the Debian packages site.

With the package name apt-get install can be used to install the prebuilt packages.

apt-get install nginx

# More than one package can be installed at a time.

apt-get install nginx nano vim vbindiff

For more information on using the various APT tools, refer to Debian's APT documentation.

Debian 12 - Setting up SSH

OpenSSH is installed in our Debian images, but by default OpenSSH does not permit logging in as the root user as a security measure. Even if logging in as root is enabled, a password must be set for the root account. Additionally, an SSH host key is required if one hasn't already been created (though this should automatically be created on the first boot).

It is generally discouraged to allow the root user to log in directly. Instead, a user account should be created, with a password set on it. No changes are needed to the OpenSSH configuration file to allow a non-root user to log in.

However, in order to login to a device as root via SSH, the following steps must occur:

sed --in-place 's/#PermitRootLogin prohibit-password/PermitRootLogin yes/' /etc/ssh/sshd_config

systemctl restart ssh.service

passwd root # Set any password

Debian 12 - Starting Automatically

A systemd service can be created to start up various applications. Create the file /etc/systemd/system/yourapp.service with the contents:

[Unit]

Description=Run an application on startup

# Uncomment the following line if networking is a dependency of the application being run

# After=network.target

[Service]

Type=simple

ExecStart=/usr/local/bin/your_app_or_script

[Install]

WantedBy=multi-user.target

The service can be started immediately and enableed on future boots with the following:

# Start the app on startup, but will not start it now

systemctl enable yourapp.service

# Start the app now, but doesn't change auto startup

systemctl start yourapp.service

See the systemd documentation for more information on how systemd services can be set up and configured.

Debian 12 - Cross Compiling

Debian provides cross compilers in their matching distribution. For example, if you are running Debian 12 on your workstation or VM:

sudo dpkg --add-architecture arm64

sudo apt-get update

# Cross compiler

sudo apt-get install gcc-aarch64-linux-gnu

# Install any needed libraries/headers from Debian 12 for arm64:

sudo apt-get install libc6-dev:arm64 libgpiod-dev:arm64

A hello world can be built with:

aarch64-linux-gnu-gcc hello.c -o hello

Tools like docker/cqfd can make this simpler to run Debian 12 in a container just for the build. See our cqfd hello world project that demonstrates a simpler way to run these from most Linux systems.

Debian 12 - Compile the aarch64 Kernel

For building kernels targeting the Debian images we recommend using cqfd. This allows building a compatible kernel using identical tools from any build host.

To build a kernel for the embeddedTS i.MX93 based platforms:

- Make sure docker is installed, and can run hello world:

- docker run hello-world

- Make sure cqfd is installed:

# Install cqfd-linux-lts builds scripts

git clone https://github.com/embeddedTS/cqfd-linux-lts

cd cqfd-linux-lts

# Clone the Linux kernel

git clone https://github.com/embeddedTS/linux-tsimx.git -b lf-6.12.y linux

# Build the kernel:

./build_tsimx93_tar.sh

This will set up the container including Debian's cross compilers, and any dependencies needed to build the kernel. This runs once on initial setup, and the only when the Dockerfile is modified. Next, it builds the defconfig, compiles the kernel, and assembles a tar of the build objects for that image. After it completes, it will print out the path to the tar file.

At this point, the tarball can be unpacked to a bootable media for the device. This can be done from a booted device, or by mounting removable media from a host Linux workstation. For example, if the root folder of the target filesystem to be updated is mounted to /mnt/, the following can be used to unpack the above tarball:

# Ensure the target filesystem is mounted to /mnt first!

# Extract kernel tarball to target filesystem,

tar xhf linux-*.tar.gz -C /mnt

| Note: | The tar h argument to tar is necessary on recent distributions that merge /usr/. Not using it will render the system unbootable. |

Ubuntu

Ubuntu 24.04 - Noble

Ubuntu 24.04 - Getting Started

This Ubuntu release is available in 2 flavors with various packages.

| Image | Estimated Size | Description |

|---|---|---|

| tsimx9-ubuntu-24.04-noble-x11-latest.tar.xz | 1640 MiB |

|

| tsimx9-ubuntu-24.04-noble-headless-latest.tar.xz | 1409 MiB |

|

| tsimx9-ubuntu-24.04-noble-minimal-latest.tar.xz | 898 MiB |

|

The default login is "user/user" which includes sudo permissions.

To write this to an SD card, first partition the SD card to have one large ext3, or ext4 partition. See the guide here for more information. Once it is formatted, extract this tar with:

# Assuming your SD card is /dev/sdc with one partition

mkfs.ext4 /dev/sdc1

mkdir /mnt/sd/

sudo mount /dev/sdc1 /mnt/sd/

sudo tar --numeric-owner -xjf tsimx9-ubuntu-24.04-noble-x11-latest.tar.xz -C /mnt/sd

sudo umount /mnt/sd

sync

To rewrite the eMMC, boot to the SD card. You cannot rewrite the emmc while it is mounted elsewhere, or used to currently boot the system. Once booted to the SD, run:

mkfs.ext4 /dev/mmcblk2p1

mkdir /mnt/emmc

mount /dev/mmcblk2p1 /mnt/emmc

wget -qO- https://files.embeddedts.com/ts-arm-sbc/ts-9370-linux/distributions/ubuntu/tsimx9-ubuntu-24.04-noble-x11-latest.tar.xz | tar --numeric-owner -xJ -C /mnt/emmc/

umount /mnt/emmc

sync

Ubuntu 24.04 - Networking

The network in Ubuntu is configured netplan. For complete documentation, see Netplan's documentation here

Some common examples are shown below. On this release network interfaces follow the predictible network interface names. Run ip addr show to get a list of the network interfaces.

Most commonly:

- end0 - Ethernet device 0 (CPU Ethernet)

- enp1s0 - Ethernet PCIe port 1 slot 0 ethernet

- usb<mac> - USB ethernet

- wlan0 - WIFI

DHCP on end0. Edit the file /etc/netplan/ethernet.yaml and add:

network:

version: 2

renderer: networkd

ethernets:

end0:

dhcp4: true

dhcp6: true

Static IP on end0. Edit the file /etc/netplan/ethernet.yaml and add:

network:

version: 2

renderer: networkd

ethernets:

end0:

dhcp4: no

addresses: [192.168.0.50/24]

gateway4: 192.168.0.1

nameservers:

addresses: [8.8.8.8,8.8.4.4]

After creating the yaml file, set the appropriate permissions and apply the netplan:

sudo chmod 600 /etc/netplan/*.yaml

sudo netplan apply

Ubuntu 24.04 - WIFI Client

Wireless configuration under Ubuntu, similar to Ethernet, also uses netplan for configuration. For example, create /etc/netplan/wifi.yaml:

network:

version: 2

renderer: networkd

wifis:

wlan0:

dhcp4: yes

dhcp6: yes

access-points:

"yourssid":

password: yourpassphrase"

After creating the yaml file, set the appropriate permissions and apply the netplan:

sudo chmod 600 /etc/netplan/*.yaml

sudo netplan apply

Ubuntu 24.04 - WIFI Access Point

hostapd needs to be installed if it is not already in order to manage the access point on the device:

apt-get update && apt-get install hostapd -y

| Note: | The install process will start an unconfigured hostapd process. This process must be killed and restarted before new hostapd.conf contents will take effect.

|

Edit /etc/hostapd/hostapd.conf to include the following lines:

interface=wlan0

ssid=YourWiFiName

wpa_passphrase=Somepassphrase

interface=wlan0

channel=7

driver=nl80211

logger_stdout=-1 # Print all module output to standard out

logger_stdout_level=2 # Print informational messages to standard out

wpa=2

wpa_key_mgmt=WPA-PSK

| Note: | Refer to the kernel's hostapd documentation for more wireless configuration options. |

To start the access point launch hostapd:

hostapd /etc/hostapd/hostapd.conf &

This will start up an access point that can be detected by Wi-Fi clients. A DHCP server will likely be desired to assign IP addresses. Refer to Debian's documentation for more details on DHCP configuration.

Ubuntu 24.04 - Installing New Software

Ubuntu provides the apt-get system which lets you manage pre-built applications. Before you do this you need to update Ubuntu's list of package versions and locations. This assumes you have a valid network connection to the internet.

apt-get update

For example, lets say you wanted to install openjdk for Java support. You can use the apt-cache command to search the local cache of Debian's packages.

root@ts-imx6:~# apt-cache search openjdk jvm-7-avian-jre - lightweight virtual machine using the OpenJDK class library freemind - Java Program for creating and viewing Mindmaps icedtea-7-plugin - web browser plugin based on OpenJDK and IcedTea to execute Java applets default-jdk - Standard Java or Java compatible Development Kit default-jdk-doc - Standard Java or Java compatible Development Kit (documentation) default-jre - Standard Java or Java compatible Runtime default-jre-headless - Standard Java or Java compatible Runtime (headless) jtreg - Regression Test Harness for the OpenJDK platform libreoffice - office productivity suite (metapackage) icedtea-7-jre-jamvm - Alternative JVM for OpenJDK, using JamVM openjdk-7-dbg - Java runtime based on OpenJDK (debugging symbols) openjdk-7-demo - Java runtime based on OpenJDK (demos and examples) openjdk-7-doc - OpenJDK Development Kit (JDK) documentation openjdk-7-jdk - OpenJDK Development Kit (JDK) openjdk-7-jre - OpenJDK Java runtime, using Hotspot Zero openjdk-7-jre-headless - OpenJDK Java runtime, using Hotspot Zero (headless) openjdk-7-jre-lib - OpenJDK Java runtime (architecture independent libraries) openjdk-7-source - OpenJDK Development Kit (JDK) source files uwsgi-app-integration-plugins - plugins for integration of uWSGI and application uwsgi-plugin-jvm-openjdk-7 - Java plugin for uWSGI (OpenJDK 7) uwsgi-plugin-jwsgi-openjdk-7 - JWSGI plugin for uWSGI (OpenJDK 7)

In this case you will likely want openjdk-7-jre to provide a runtime environment, and possibly openjdk-7-jdk to provide a development environment.

Once you have the package name you can use apt-get to install the package and any dependencies. This assumes you have a network connection to the internet.

apt-get install openjdk-7-jre

# You can also chain packages to be installed

apt-get install openjdk-7-jre nano vim mplayer

For more information on using apt-get refer to Ubuntu's documentation here.

Ubuntu 24.04 - Setting up SSH

To install ssh, install the package as normal with apt-get:

apt-get install openssh-server

Make sure the device is configured on the network and set a password for the remote user. SSH will not allow remote connections without a password or a valid SSH key pair.

passwd root

| Note: | The default OpenSSH server will not permit root to login via SSH as a security precaution. To allow root to log in via ssh anyway, edit the /etc/ssh/sshd_config file and add the line PermitRootLogin yes in the authentication section. This change will take effect after reboot or after sshd service restart.

|

After this setup it is now possible to connect from a remote PC supporting SSH. On Linux/OS X this is the "ssh" command, or from Windows using a client such as PuTTY.

| Note: | If a DNS server is not present on the target network, it is possible to save time at login by adding "UseDNS no" in /etc/ssh/sshd_config. |

Ubuntu 24.04 - Starting Automatically

A systemd service can be created to start up various applications. Create the file /etc/systemd/system/yourapp.service with the contents:

[Unit]

Description=Run an application on startup

# Uncomment the following line if networking is a dependency of the application being run

# After=network.target

[Service]

Type=simple

ExecStart=/usr/local/bin/your_app_or_script

[Install]

WantedBy=multi-user.target

The service can be started immediately and enableed on future boots with the following:

# Start the app on startup, but will not start it now

systemctl enable yourapp.service

# Start the app now, but doesn't change auto startup

systemctl start yourapp.service

See the systemd documentation for more information on how systemd services can be set up and configured.

Ubuntu 24.04 - Cross Compiling

Ubuntu 24.04 - Compile the aarch64 Kernel

For building kernels targeting the Debian images we recommend using cqfd. This allows building a compatible kernel using identical tools from any build host.

To build a kernel for the embeddedTS i.MX93 based platforms:

- Make sure docker is installed, and can run hello world:

- docker run hello-world

- Make sure cqfd is installed:

# Install cqfd-linux-lts builds scripts

git clone https://github.com/embeddedTS/cqfd-linux-lts

cd cqfd-linux-lts

# Clone the Linux kernel

git clone https://github.com/embeddedTS/linux-tsimx.git -b lf-6.12.y linux

# Build the kernel:

./build_tsimx93_tar.sh

This will set up the container including Debian's cross compilers, and any dependencies needed to build the kernel. This runs once on initial setup, and the only when the Dockerfile is modified. Next, it builds the defconfig, compiles the kernel, and assembles a tar of the build objects for that image. After it completes, it will print out the path to the tar file.

At this point, the tarball can be unpacked to a bootable media for the device. This can be done from a booted device, or by mounting removable media from a host Linux workstation. For example, if the root folder of the target filesystem to be updated is mounted to /mnt/, the following can be used to unpack the above tarball:

# Ensure the target filesystem is mounted to /mnt first!

# Extract kernel tarball to target filesystem,

tar xhf linux-*.tar.gz -C /mnt

| Note: | The tar h argument to tar is necessary on recent distributions that merge /usr/. Not using it will render the system unbootable. |

Yocto

The Yocto Project is a framework for creating customized, production-grade Linux systems specifically geared toward embedded devices. It provides a flexible set of tools, metadata, and build definitions that allow developers to assemble complete Linux images tailored to purpose-built hardware, strict resource limits, and long product lifecycles. Its build system, based on OpenEmbedded and BitBake, enables deterministic image generation

Yocto emphasizes reproducibility, maintainability, and scalability for long-term embedded deployments. Its layered architecture allows hardware support, policy decisions, and application logic to be separated cleanly, making it easier to maintain products across multiple hardware revisions or market variants. The project also includes mechanisms for generating toolchains and SDKs, along with integrated SPDX license data and Software Bills of Materials (SBOMs) to support compliance, supply-chain visibility, and regulatory requirements.

Yocto NXP - Walnascar Overview

The NXP Semiconductors Yocto BSP provides strong hardware support for NXP System-on-Chip (SoC) platforms. For full details, see the NXP Yocto User Guide. This BSP provides NXP’s recipes for their own forks of U-Boot and the Linux kernel. NXP's Yocto fork provides NXP's forks of some mainline drivers that provide full featured hardware enablement before the mainline Linux/U-Boot reach parity.

Our support builds on this base. We define our own machine configurations, use our fork of NXP’s kernel and U-Boot for our boards, and include a few small utilities to support our hardware.

Yocto NXP - Walnascar Create Image

This section describes how to build a Yocto image for the TS-9370 using the NXP Walnascar BSP and the embeddedTS Yocto layer. The layer used for TS-9370 support is available here: [1](https://github.com/embeddedTS/meta-ts-nxp)

The steps below follow the standard NXP Walnascar workflow, with the additional requirement of adding the meta-ts-nxp layer to enable embeddedTS board support.

Install the Google repo tool:

mkdir ~/bin

curl http://commondatastorage.googleapis.com/git-repo-downloads/repo > ~/bin/repo

chmod a+x ~/bin/repo

# Add this to your shell path (or include it in ~/.bashrc)

PATH=${PATH}:~/bin

Download the NXP Walnascar BSP

Create a working directory and download the NXP manifest:

mkdir walnascar

cd walnascar

repo init -u https://github.com/nxp-imx/imx-manifest -b imx-linux-walnascar -m imx-6.12.34-2.1.0.xml

repo sync

Add the embeddedTS Yocto Layer

git clone https://github.com/embeddedTS/meta-ts-nxp.git -b walnascar sources/meta-ts-nxp/

ln -sf sources/meta-ts-nxp/tsimx-setup-release.sh imx-setup-release.sh

This layer provides the ts9370 machine definition, our fork of NXP's kernel and U-Boot, and the supporting utilities required for TS-9370 builds.

Configure the machine and distribution, then initialize the build directory:

MACHINE=ts9370 DISTRO=fsl-imx-xwayland source ./imx-setup-release.sh -b bld-xwayland

Build the full Yocto image:

bitbake imx-image-full

The output images will appear in:

tmp/deploy/images/ts9370/

These artifacts include the kernel, bootloader, root filesystem, and all files needed to deploy a Walnascar-based Yocto system on the TS-9370.

Yocto NXP - Walnascar mfgtools

To use the NXP mfgtools (uuu) to flash the SOM, it needs to connect as a USB device to the development machine. Connect a TC2030-USB cable to CN66. This connector is on the corner near the type A USB. Keep in mind this is run in parallel with the top port of J2 which should not have anything connected while CN66 is connected.

The relevant outputs of the yocto build are the imx-boot bootloader container and the compressed disk image which ends in '.wic.zst' depending on which image is built. uuu needs the uncompressed file though so use zstd utility to decompress the .wic.zst file first.

Flashing the yocto build is similar to the process in U-boot Development except uuu is used to flash both the bootloader and the disk image. It requires the wizusb utility and the uuu utility from the mfgtools repo.

Install the dependencies on your Linux Workstation:

- wizusb

- access to Wizard registers over USB

- NXP mfgtools

- uuu tool for booting/flashing i.MX93 over USB

To load the yocto build output on the board, run:

# Switch boot to USB Serial Downloader

wizusb 17 0x1

# Reset the board, so it comes up in the new strapping

wizusb 8 0x1

# Boot, Program u-boot and disk image over USB:

uuu -brun emmc_all imx-boot imx-full-image.wic

# Switch boot to USDHC1 8-bit eMMC

wizusb 17 0x2

# Reset the board, so it comes up in the new strapping

wizusb 8 0x1

Yocto Mainline BSP

The mainline bsp is pending kernel support in linux-lts and then will follow up in meta-ts, and our kas configs in ts-oe-bsp.

Yocto SDK

From the yocto build system, bitbake can create an SDK installer that can be used on other systems to compile applications that will run on the target hardware. To create the SDK installation script:

bitbake -c populate_sdk imx-image-full

Where imx-image-full is whatever image is installed on the target hardware. This will add all necessary libraries from that image for cross-compiled binaries to link against. When that bitbake completes, you will end up with a very large (5GB) installation shell script in tmp/deploy/sdk/ directory. Executing that shell script as root will install the SDK into /opt by default.

To use the SDK after installing it on a host, source the SDK's environment file:

. /opt/fsl-imx-wayland/6.12-walnascar/environment-setup-armv8a-poky-linux

This sets environment variables such as $CC and $CROSS_COMPILE so that you should be able to run any build system (make, autoconf, cmake) as normal and build an aarch64 binary linked against the library versions in the target image, which can be copied over to target hardware for testing.

See yocto sdk manual for reference.

Buildroot

The full-featured Debian image may be too cumbersome for some applications. Applications that require faster bootup time or a smaller root filesystem will benefit greatly from using a lighter distribution like Buildroot. Using Buildroot for generating images makes it easy to keep software up to date, both userspace and kernel. Additionally, the use of Buildroot allows for building full images completely from source, with semi-reproducable builds, and full software license reports.

To assist customers heading down this path, we maintain our own Buildroot br2-external tree. This tree includes upstream Buildroot as a submodule, which eases updating between Buildroot releases. See the Buildroot manual for more information on Buildroot and br2-external trees.

In order to provide an easy transition from a larger Linux distribution to Buildroot, we provide and maintain two levels of configurations:

- The base configuration for each device brings in hardware support to get the unit booted, but offers minimal software support and relies mostly on tools provided by BusyBox.

- An "extra packages" defconfig that can be merged in with any of the base configurations in order to provide many additional packages to create an environment that is more consistent with larger Linux distributions.

The larger Buildroot configuration averages about 10 seconds of boot time, much of which is spent on networking. The base configurations can reduce this time significantly.

Our Buildroot br2-external currently uses the lf-6.12.y branch of our Linux i.MX kernel repository for the i.MX 9x devices.

| Note: | Note that our base configurations include that device's utilities package where possible. Normally, these utilities (e.g. tshwctl, tsmicroctl, etc.) list the git hash of the build source in the help output. However, due to the Buildroot process, the git hash in these utilities reflects the git hash of Buildroot-ts, NOT of the utilities repository. There is no way to work around this without building the utilities outside of Buildroot.

|

Buildroot - Installing

When building Buildroot from source, the output files can be used to create a bootable eMMC rootfs for the TS-9370. The output files are also compatible with our USB Image Replicator.

The default configuration was designed to be close to our stock Debian distribution.

Buildroot - Building

Buildroot is intended to be completely cross-compiled from a host Linux workstation. This process creates a cross-compiler which is then used to build all target applications, kernel, etc., and then output a bootable image / tarball. The following instructions will create a bootable image / tarball for the target system:

Clone the repository:

git clone --recurse-submodules https://github.com/embeddedTS/buildroot-ts.git

cd buildroot-ts/

Configure the build:

# The following command uses a Buildroot script to merge two config files.

# The extra_packages_defconfig includes more usual packages to match our stock images

./buildroot/support/kconfig/merge_config.sh technologic/configs/extra_packages_defconfig technologic/configs/tsimx9_defconfig

# A smaller base image can be made with bare hardware support using:

# make tsimx9_defconfig

At this point, the default configuration can be modified if desired:

make menuconfig

And finally, start the build process:

make

The Buildroot process can take a large amount of time to build depending on available system resources. Note that if any changes occur in the config file, it is recommended to clean the build tree and start the process over. Buildroot ccache is not enabled by default, but can be to help speed up repeated builds. See the Buildroot manual for more information about ccache and Buildroot.

Once it is finished building, Buildroot will output a filesystem tarball to buildroot/output/images/rootfs.tar.xz. This file can be used with the Installing Buildroot instructions to get this tarball booted on the target device.

Buildroot - Cross Compiling

In order to generate a cross-compiler from Buildroot, first configure the target build as outlined in the first steps of the build instructions. Once configured, a separate make command can be issued to generate a tarball package of the cross-compiler. This can be unpacked to any location on the host Linux workstation's filesystem and then used to cross-compile additional applications for the target. The build, setup, and use of the cross-compiler can be done with the following steps:

# Be sure the target is configured first!

# The following command will output the cross-compiler package as well as build the target image completely if not built already

make sdk

# Unpack the tarball to new directory in the users home directory

# Note that the tarball name may be slightly different depending on how the toolchain is configured in Buildroot

mkdir ~/buildroot-toolchain

tar xf buildroot/output/images/arm-buildroot-linux-gnueabihf_sdk-buildroot.tar.gz -C ~/buildroot-toolchain/

# Update the path information for the toolchain (must be done when the tarball is unpacked, or if the root folder of the toolchain is moved!)

# Note that, as above, the path for the compiler may be slightly different depending on how the toolchain is configured in Buildroot

~/buildroot-toolchain/arm-buildroot-linux-gnueabihf_sdk-buildroot/relocate-sdk.sh

# Create a simple Hello World application source

cat << EOF > hello.c

#include <stdio.h>

void main(void) { printf("Hello!\n"); }

EOF

# Build a binary from the Hello World source that can be run on the target device

~/buildroot-toolchain/arm-buildroot-linux-gnueabihf_sdk-buildroot/bin/arm-linux-gcc hello.c -o hello

# This cross compiler can be added to the user's PATH variable for easy access

export PATH=$PATH:~/buildroot-toolchain/arm-buildroot-linux-gnueabihf_sdk-buildroot/bin

arm-linux-gcc hello.c -o hello

The hello binary can then be copied to the target device and executed on it.

Note that the make sdk command can be run at any time to generate the toolchain tarball. Even after Buildroot has generated the output image.

Buildroot is extremely flexible in its generation and use of a cross-compiler. See the Buildroot manual for more information on advanced use of the Buildroot generated toolchain as well as using Buildroot's generated cross-compiler as an external compiler for Buildroot.

Buildroot - Configuring Network

Buildroot implements the ip, ifconfig, route, etc., commands to manipulate the settings of interfaces. The first Ethernet interface is set up to come up automatically with our default configuration. The interfaces can also be manually set up:

# Bring up the CPU network interface

ifconfig eth0 up

# Set an IP address (assumes 255.255.255.0 subnet mask)

ifconfig eth0 192.168.0.50

# Set a specific subnet

ifconfig eth0 192.168.0.50 netmask 255.255.0.0

# Configure a default route. This is the server that provides an internet connection.

route add default gw 192.168.0.1

# Edit /etc/resolv.conf for the local DNS server

echo "nameserver 192.168.0.1" > /etc/resolv.conf

Most commonly, networks will offer DHCP which can be set up with one command:

# To setup the default CPU Ethernet port

udhcpc -i eth0

# All Ethernet ports can be made active and request DHCP addresses with:

udhcpc

To have network settings take effect on startup in Buildroot, edit /etc/network/interfaces:

# interface file auto-generated by Buildroot

auto lo

iface lo inet loopback

auto eth0

iface eth0 inet dhcp

pre-up /etc/network/nfs_check

wait-delay 15

Note that the default network startup may timeout on some networks, e.g. network protocols such as STP can delay packet movement. This can be resolved in Buildroot by adding network configuration options to fail after a number of attempts (rather than a timeout) or retry for a DHCP lease indefinitely. For example, adding one of the following lines under the iface eth0 inet dhcp section:

udhcpc_opts -t 0to infinitely retryudhcpc_opts -t 5to fail after five attempts.

See the man page for interfaces(5) for further information on the syntax of the interfaces file and all of the options that can be passed.

For more information on network configuration in general, Debian provides a great resource here that can be readily applied to Buildroot in most cases.

Buildroot - Installing New Software

Buildroot does not include a package manager by default (though it is possible to enable one). This means installing software directly on the platform can be cumbersome and is not the intended path when using Buildroot. It is recommended to modify the Buildroot configuration to include additional packages. See the Building Buildroot section for information on modifying the configuration to build additional packages.

If a desired package is not available in Buildroot, there are a number of options available moving forward. It is possible to add packages to the build process, though this does require some knowledge of Buildroot internals. Another option is to use the cross compiler that is output by Buildroot in order to compile packages on a host system and then copy them over to the target. It is also possible to install a toolchain directly on the device, and compile applications natively. The last option is the least recommended as it greatly increases the final image size and adds unnecessary complexity.

Buildroot - Setting Up SSH

The default configuration has Dropbear set up. Dropbear is a lightweight SSH server.

Make sure the device is configured on the network and set a password for the remote user. SSH will not allow remote connections without a password set. The default configuration does not set a password for the root user, nor are any other users configured.

passwd root

After this setup it is now possible to connect from a remote PC supporting SSH. On Linux/OS X this is the ssh command, or from Windows using a client such as PuTTY.

Buildroot - Starting Automatically

Buildroot defaults to using the BusyBox init system, and all of our provided configurations use this as well. The following custom startup script uses this format. For information on other init systems that Buildroot can use, as well as creating startup scripts for these, see the Buildroot manual.

The most straightforward way to add an application to startup is to create a startup script. This example startup script that will toggle the red LED on during startup, and off during shutdown. In this case the script is named customstartup which can be changed as needed.

Create the file /etc/init.d/S99customstartup with the following contents. Be sure to set the script as executable!

#! /bin/sh

# /etc/init.d/customstartup

case "$1" in

start)

echo 1 > /sys/class/leds/red-led/brightness

## If you are launching a daemon or other long running processes

## this should be started with

# nohup /usr/local/bin/yourdaemon &

;;

stop)

# if you have anything that needs to run on shutdown

echo 0 > /sys/class/leds/red-led/brightness

;;

*)

echo "Usage: customstartup start|stop" >&2

exit 3

;;

esac

exit 0

| Note: | The $PATH variable is not set up by default in init scripts so this will either need to be done manually or the full path to your application must be included. |

Buildroot provides numerous mechanisms to create this file in the target filesystem at build time. See the Buildroot manual for more information on this.

This script will be automatically called at startup and shutdown thanks to the file location and naming. However, it can also be manually started or stopped:

/etc/init.d/S99customstartup start

/etc/init.d/S99customstartup stop

Backup / Restore

While all of our products ship with images pre-loaded in to any supplied media, there are many situations where new images may need to be written. For example, to restore a device to its factory settings or apply a customized image/filesytem for application deployment. Additionally, specific units may be used for development and that unit's disk images need to be replicated to other units to be deployed in the field.

We offer a number of different ways to accomplish both capturing images to be written to other units, and the actual writing process itself. See the sections below for details on our USB Image Replicator tool to capture and/or write images, as well as details on manual processes to capture and write images on each of this device's media.

Image Replicator

This platform supports our Image Replicator tool. The Image Replicator tool is intended for use by developers as a means to write bootable images or filesystems onto a device's media (SD / eMMC / SATA / etc.) as part of the developer's production or preparation process. In addition to writing media, the Image Replicator tool can capture images from a device's media and prepare them to be written to other devices.

The Image Replicator tool is a USB disk image that boots from a target device to capture or write USB drive-resident media directly onto the target without a host workstation. It runs from a USB drive and allows:

- Capturing an image of the device storage (eMMC/microSD)

- Writing an existing image back to media

- Creating bootable media for mass deployment

The USB disk image is based on Buildroot and contains a set of scripts that handle the capture and write processes. The processes and scripts are flexible, can be used as-is, or adapted into larger production processes to format and load data onto devices. A single USB drive can be used to capture images from a device and then, once inserted in to other devices, write those same images onto other devices. The capture process is not necessary if it is not needed. Images for the target device can be copied to the USB drive, booted on compatible units, and have the target images written to that unit's media.

Image Capture Process

The image capture process performs the following steps. For more detailed information, see the Image Capture section below.

- If no valid images exist on the disk, image capture starts.

- For each valid media present on the unit, a bit for bit copy of the source is made.

- This image is mounted, sanitized (to remove unneeded files and allow safe copying of the image to other units), and saved as either a disk image or a tarball, depending on the partition layout of the source disk.

- All images and tarballs are compressed, with both the output files' MD5 hash saved, as well as all of the files contained in the root partition (MD5 hashes saved) to a file for later verification.

The captured images and tarballs are named such that the USB Image Replicator disk can be immediately used to boot another unit and have it perform the Image Write process, writing that unit's media with the captured images.

| Note: | When using this process, the USB drive used for the Image Replicator must be sized large enough to handle multiple compressed images as well as the uncompressed copy of an active media image. If the image capture process runs out of space, the process indicates a failure. |

Image Write Process

The image write process performs the following steps. For more detailed information see the Image Write section below.

- For each valid media present on the unit, find the first valid source image file for it.

- If a source image exists for a media that is not present on the unit, then the process indicates a failure.

- If the source image is a tarball, format the target disk with an appropriate file system and unpack it to the target disk, verifying all files against the MD5 hash file list after they are written.

- If the source image is a disk image, write that to the target disk. If an MD5 file for the disk image exists, read back the written disk and compare it to the hash.

Creating a USB Image Replicator Disk

Image Replicator USB disk images can be found below:

Disk image: tsimx9-usb-image-replicator.dd.xz

Tarball: tsimx9-usb-image-replicator-rootfs.tar.xz

Two types of USB Image Replicator images are available for this platform: a tarball and an actual disk image. They both have the same contents yet provide different methods to write the Image Replicator tool to a USB disk.

- Disk Image (.dd.xz)

- The disk image is easier to write from different workstation OSes, will auto-expand to the full disk length on its first boot, and is intended to be used for image capture (and later image writing) due to its small size and auto-expansion process. We recommend this route for users who may not have access to a Linux workstation or need to capture images from a golden unit first.

- Tarball Image (.tar.xz)

- The tarball image is easiest to write from a Linux workstation, but requires creating a partition table on the USB disk (if one does not already exist), formatting the filesystem, and unpacking the tarball. It can readily be used for both image capture and writing, but is easiest when image capture is not needed, due to the auto-expansion process.

| Note: | This process recommends a solid-state USB drive. Slower USB drives, especially those with spinning media, may take too long to enumerate and the bootloader will not boot the Image Replicator disk. Low quality, damaged, and/or worn out USB drives may cause unexpected errors that appear unrelated to the USB drive itself. If there are issues using the Image Replicator, we recommend first trying a new, fresh, high-quality USB drive from a trusted brand. |

Disk Image

This process uses a small disk image that can be written to a USB device. This disk image uses an ext3 filesystem which expands on its first boot to the full length of the disk before beginning the image capture process, and is recommended for users who may not have access to a Linux workstation or who need to capture images from a golden unit.

It is possible to use the disk image only for image writing. However, to ensure that full disk space is available, it is recommended to write the disk image to a USB drive, set the IR_NO_CAPTURE_* Image Replicator Runtime Options, boot it on the target unit, let the system boot and expand to the disk, insert the USB drive back in to a workstation, and then copy in the desired image files for the target unit from the workstation.

Writing Disk Image From a Linux Workstation

The disk image can be written via the command line with the dd command (replace /dev/sdX with the correct USB device node):

xzcat <platform>-usb-image-replicator.dd.xz > /dev/sdX

Graphical tools also exist for this purpose, for example balenaEtcher[1] offers this functionality.

Writing Disk Image From a Windows Workstation

A number of tools exist for writing an image to a USB drive, including (but not limited to) balenaEtcher[1] and Win32DiskImager[2]

Writing Disk Image From a MacOS Workstation

We recommend using a tool such as balenaEtcher[1] to write disk images.

Tarball

This process is easiest on a Linux workstation, but can be performed on other operating systems so long as they can support a compatible filesystem, the xz compression algorithm, as well as the tarball archive format. Note that in many cases, one of our computing platforms running our stock Linux image can be used if a Linux workstation is not available. After writing the tarball to a USB disk, the full length of the USB disk would be available to copy source images, to write them to other units.

The image replicator and scripts require a minimum of 50 MB. Additionally, the size of target disk images or tarballs used also dictate the minimum USB disk size required. The USB drive should have only a single partition, which is formatted ext2[1] / 3 / 4[2] or FAT32/vfat[3] Note that other filesystems are not compatible with U-Boot and therefore cannot be used.

Writing Tarball From a Linux Workstation

# This assumes USB drive is /dev/sdc:

sudo mkfs.ext3 /dev/sdc1

sudo mkdir /mnt/usb/

sudo mount /dev/sdc1 /mnt/usb/

sudo tar --numeric-owner -xf /path/to/<platform>-usb-image-replicator-rootfs.tar.xz -C /mnt/usb/

sudo umount /mnt/usb/

Writing Tarball From a Windows Workstation

A third party tool is recommended, as native Windows archive tools have occasionally not worked correctly. Tools such as 7-Zip[4] or PeaZip[5] are known working. (It may also be possible to use Windows Subsystem for Linux following the Linux Workstation instructions above, but this has not been tested.)

Note that some Windows tools may attempt to use the whole disk, rather than create a partition table. A partition table with a single partition is required for U-Boot support.

With a formatted USB disk, the archive can be unpacked to the root folder of the USB disk. Be sure to not unpack the tarball contents into a new folder on the drive, as this will not boot.

- ↑ The ext2 filesystem has a max file size limit as low at 16 GiB. This may cause issues for Image Capture.

- ↑ . Use of ext4 may require additional options. U-Boot on some platforms does not support the 64-bit addressing (added as default) in recent revisions of

mkfs.ext4. If using e2fsprogs 1.43 or newer, the options-O ^64bit,^metadata_csummay need to be used with ext4 for proper compatibility. Older versions of e2fsprogs do not need these options passed, nor are they needed for ext2 / 3. - ↑ . The FAT32 (supported by vfat in Linux) filesystem has a max file size limit of 4 GiB. This may cause issues for Image Capture.

- ↑ embeddedTS is not affiliated with this tool. 7-Zip 21.07 tested in Windows 10 on 20220222

- ↑ embeddedTS is not affiliated with this tool. PeaZip 7.2.0 tested in Windows 10 on 20220222

Running the Image Replicator Tool

Once a USB drive is formatted with the Image Replicator tool (see Creating a USB Image Replicator Disk for the correct files and process), boot to this USB drive (note that the Image Replicator already sets up the correct U-Boot boot scripts to boot to the USB drive, see the aforementioned section for details on how to make U-Boot call the scripts on the USB drive). This will start either image capture if no disk images/tarballs are present on the USB drive, or image write if there are disk images/tarballs present on the USB drive.

Image Replicator Runtime Options

Some of the runtime operations of the Image Replicator can be specified. These are handled by creating empty files in the root folder of the bootable USB drive. When booted, these files are analyzed and actions taken based on them.

| Option | Description |

|---|---|

|

|

When capturing, skip media-matching this name. See the respective platform manual for information on which names correspond to which physical media. Note that the names are generic and match what the media is captured as, regardless of actual device node. The names are uniform between capture and write for a given system. |

IR_NO_COMPRESS

|

When capturing, do not compress the data. On slower systems, slower disks, or systems with a large amount of data to capture, the final compression can take a significant amount of time. This option will allow a capture, but will not attempt to compress it. |

IR_SHELL_ONLY

|

When booting, skip doing any of the image replication process (Capture or Write) and instead drop to a login prompt. Useful for debugging. Note that, to prevent any confusion the system will indicate a non-critical failure when skipping any of the Image Replication process. |

Image Replicator LED Status

The green and red LEDs of the platform are used to indicate status.

Any LED patterns not matching the table below indicate different operational states of the platform itself, e.g. executing the bootloader, the kernel is running but Image Replicator has not yet started, etc.

| Green | Red | State | Description |

|---|---|---|---|

| Short Strobe | Solid | Running | The Image Replicator process is running. |

| 0.5 Hz Blink | Off | Succeeded | All operations being performed by the Image Replicator have completed successfully. |

| Off | 0.5 Hz Blink | Non-critical Failure | One or more operations being performed by the Image Replicator have failed to complete. View logs in /tmp/logs/ as well as the failure reason in /tmp/failed

|

| Off | 4 Hz Blink | Critical Failure | An operation has failed in a way that could leave the device inoperable if power were to be removed. View logs in /tmp/logs as well as the failure reason in /tmp/failed.

|

Image Capture

If no valid images to write exist on the booted USB Image Replicator drive, the image capture process starts automatically.

Note that while in progress, the USB Image Replicator drive is mounted read-write. Do not remove power or disconnect the USB Image Replicator drive until the whole process has completed.

To help diagnose failures, files in /tmp/logs/ contain output from each capture process.

For each media present on the unit (SD / eMMC / SATA / etc.), the image capture process will do the following:

- Copy the entire media image to an appropriately named file on the USB Image Replicator drive, e.g.

sdimage.dd. No data is written to the source media and it is never mounted. The source disk can follow the stock partition layout, or implement a customized one. - Perform an fsck on the Linux rootfs partition in the image file. Note that, if deviating from the standard partition layout, it may be necessary to modify the scripts handling the capture process.

- Mount the Linux rootfs partition from the image file and sanitize the filesystem. The sanitization process removes temporary files (e.g.

/log/files), unique files (e.g. ssh private key files, machine ID files), adds a file to indicate that it is a custom image with the date as its contents, etc. The full list of operations can be found in this script. It may be necessary to modify this file for unique situations. - If the media's partition layout uses only a single partition, the filesystem is packed in to a tarball on the USB Image Replicator drive which is appropriately named and compressed, e.g.

sdimage.tar.xz. The image file is then unmounted and removed from the USB Image Replicator drive. - If the media's partition layout uses multiple partitions, the image file is then unmounted, an md5sum of the image file taken, compressed and appropriately named on the USB Image Replicator drive, e.g.

emmcimage.dd.xz, and then an md5sum of the compressed image is taken.

Note that when using this process, the USB Image Replicator drive that is used must be sized large enough to handle multiple compressed images as well as the uncompressed copy of the media image actively being worked with. If the image capture process runs out of space, the process will indicate a failure via the LEDs.

The images files captured are saved to the root folder of the USB Image Replicator drive. Upon completion, it is safe to remove power or unplug the USB drive.

For more details on the image capture process, see this script.

Image Write

This process is used to write existing images to media on a target unit. If appropriately named disk images or tarballs (see table below) are present in the root folder of the USB Image Replicator drive when booted, then the startup scripts will start the image writing process. The latest disk images we provide for our platforms can be downloaded from our FTP site, see the backup and restore section for links to these files.

Note that the USB Image Replicator drive remains read-only through the entire process but target devices may be mounted or actively written. It is not advised to remove power or disconnect the USB Image Replicator drive until the whole process has completed.

To help diagnose failures, files in /tmp/logs/ contain output from each writing process.

The Image Replicator script expects disk images or tarballs to have specific names to match the target media. The script will attempt to match tarball and then disk image names (in the order they are listed in the table below) for each target media, using the first file that is found to write to the target media. Note that symlinks can be used on the USB Image Replicator disk if formatted with a filesystem that supports symlinks. This can be used, for example, to write the same tarball to both SD and eMMC from only a single copy of the source tarball.

Upon completion, it is safe to remove power or unplug the USB drive.

For more details on the image write process, see this script.

The following table is the list of valid file names and how they are processed:

| Target media | Accepted filenames | Description |

|---|

| SD Card |

|

Tar of the filesystem. This will repartition the SD card to a single partition and extract this tarball to the filesystem. If present, a file named /md5sums.txt in the tarball will have its contents checked against the whole filesystem after the tarball is extracted. This md5sums.txt file is optional and can be omitted, but it must not be blank if present. This file is present in our official images and is created during image capture with the Image Replicator tool.

|

|---|---|---|

|

|

Disk image of the media. This will be written to the SD card block device directly. If present on the USB Image Replicator drive, a file named /sdimage.dd.md5 will be used to verify the data written to the SD card against this checksum. This file is provided with our official images and is created during image capture with the Image Replicator tool.

|

| eMMC |

|

Tar of the filesystem. This will repartition the eMMC to a single partition and extract this tarball to the filesystem. If present, a file named /md5sums.txt in the tarball will have its contents checked against the whole filesystem after the tarball is extracted. This md5sums.txt file is optional and can be omitted, but it must not be blank if present. This file is present in our official images and is created during image capture with the Image Replicator tool.

|

|---|---|---|

|

|