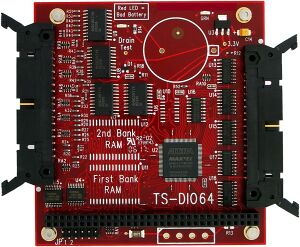

TS-DIO64

| |

| Product Page | |

| Documents | |

|---|---|

| Schematic | |

| Mechanical |

Overview

The TS-DIO64 is an 8-bit PC/104 (standard format) peripheral board that provides 64 digital I/O points (32 inputs plus 32 outputs) through two 34-pin locking connectors that are compatible with ribbon cables. Up to 4 TS-DIO64 boards may be installed into a single system, enabling up to 256 DIO points (128 inputs plus 128 outputs).

The optional battery-backed SRAM is decoded in ISA memory space at a location determined by the SRAM control register (see Register Map).

| Note: | The Battery-backed SRAM option is only designed to work with the TS-7000 series SBC's (TS-ARM products only). |

LEDs

The on-board red LED indicates the Lithium battery health. Typical lifetime of the battery is over 10 years. When the red LED is ON, the battery needs replacement, but this does not mean that the battery-backed RAM contents are corrupted. The battery can be purchased from Digikey, part number #P340-ND (Panasonic manufacturer part number is #CR2450).

The on-board green LED is an SRAM activity indicator. It pulses during read/write activity on the PC/104 bus.

I/O Address Selection

| I/O Address | JP1 | JP2 |

|---|---|---|

| 0x100 | Off | Off |

| 0x110 | On | Off |

| 0x120 | Off | On |

| 0x130 | On | On |

| Note: | PC104 base address space for TS ARM SBC is not fixed at 0x0000. Please refer to your SBC documentation for the correct 8 or 16 bit access page base addresses for PC104. The above addressing would be added to the SBC's base PC104 address, for example if the SBC's PC104 base address is 0xEE000000, and both jumpers are off, the board address would be 0xEE000100. |

Register Map

The TS-DIO64 uses 16 registers of 8-bits each (16 bytes total) which appear at the jumpered I/O base address. All input and output DIO registers are initialized at power up or system reset to zero by default.

| Address | Bits | Access | Description |

|---|---|---|---|

| BASE + 0x0 | 7:0 | Read Only | Board identifier (returns 0xA4) |

| BASE + 0x1 | 7:5 | Read Only | Reserved |

| 4 | Read Only | SRAM option present (1 = on) | |

| 3:0 | Read Only | PLD Revision (1=REVA) | |

| BASE + 0x2 | 7:5 | Read/Write | Reserved |

| 4 | Read/Write | Use SRAM in memory space (1 = enabled) | |

| 3:2 | Read/Write | SRAM memory address decode [1]

0 = 0x0 1 = 0x20_0000 2 = 0x30_0000 | |

| 1 | Read Only | Battery status (1 = ok, 0 = bad) | |

| 0 | Read Only | External power status (1 = on) | |

| BASE + 0x3 | 7:0 | Read Only | Reserved |

| BASE + 0x4 | 7:0 | Read/Write | Output pins 1:8 |

| BASE + 0x5 | 7:0 | Read/Write | Output pins 9:16 |

| BASE + 0x6 | 7:0 | Read/Write | Output pins 17:24 |

| BASE + 0x7 | 7:0 | Read/Write | Output pins 25:32 |

| BASE + 0x8 | 7:0 | Read Only | Input pins 1:8 |

| BASE + 0x9 | 7:0 | Read Only | Input pins 9:16 |

| BASE + 0xa | 7:0 | Read Only | Input pins 17:24 |

| BASE + 0xb | 7:0 | Read Only | Input pins 25:32 |

- ↑ Note ISA Bit 21 is nonstandard but must be set or cleared for by the host computer as applicable for memory access to function. See the PC104 connector section for details.

Connectors

Input Connector

On the 34-pin input connector (CN4), pins 1 to 32 are used for 32 total digital inputs. Any voltage above 3.0 volts on the input pins will return a logic "1", while any voltage below 1.2 volts will return a logic "0". Each input can be driven from 0 to +30V, and all inputs have a 4.7K ohm resistor pull-up to 5V.

The input connector will follow this pinout:

| 33 | 31 | 29 | 27 | 25 | 23 | 21 | 19 | 17 | 15 | 13 | 11 | 9 | 7 | 5 | 3 | 1 |

| 34 | 32 | 30 | 28 | 26 | 24 | 22 | 20 | 18 | 16 | 14 | 12 | 10 | 8 | 6 | 4 | 2 |

| Note: | See the white dot, or the square pad on the bottom of the PCB to find pin 1. |

| Note: | Pin 33 is fused 5V and the current is limited with a PolyFuse to 750 mA. Pin 34 is ground. These pins are not input signals. |

Output Connectors

On the 34-pin output connector (CN3), pins 1 to 32 are used for 32 total digital outputs. Pin 33 is clamp voltage and pin 34 is ground. 22 outputs (pins 1 to 22) can sink 200 mA, while 10 outputs (pins 23 to 32) can sink 400 mA. These can be mounted in parallel to get much higher current drive. All outputs pins can sink up to 40V loads.

Writing a logic "1" to the output register bits will turn on the sink darlington transistor, forcing the output to below 1.2V. Writing a logic "0" will turn off the sink darlington transistor, and the output will be floating (not forced high). All output registers are initialized to zero at power up or system reset, which means that all outputs are turned off by default (not sinking current).

| Note: | The clamp pin should be connected to the highest voltage being used for loads. For example, if the outputs are driving 24V solenoids and 12V relays, then pin 33 should be connected to the 24V power supply. This will protect the output transistors from reverse EMF "transients" that may exceed 40V if the clamp pin was not connected to 24V. |

The output connector will follow this pinout:

| 33 | 31 | 29 | 27 | 25 | 23 | 21 | 19 | 17 | 15 | 13 | 11 | 9 | 7 | 5 | 3 | 1 |

| 34 | 32 | 30 | 28 | 26 | 24 | 22 | 20 | 18 | 16 | 14 | 12 | 10 | 8 | 6 | 4 | 2 |

| Note: | See the white dot, or the square pad on the bottom of the PCB to find pin 1. |

PC104 Connector

The TS-DIO64 PC104 connector is not 100% adherent to the PC104 standard. Some design notes should be taken into account before connecting or using this device. Below is a pin description for the PC104 connector. Signals of particular note are pin B10, which is tied to system ground, and the upper-order address pins ISA_ADD_18 through ISA_ADD_21. PC104 pin B10, in the PC104 specification, is a +12V key voltage. This peripheral should NOT be used in conjunction with any peripheral that injects 12 volts onto PC104 pin B10. PC104 pin B19 is not normally an address bit, the TS-DIO64 uses this (along with signals ISA_ADD_18 through 20) as the most significant address bit during mem bus cycles, so it is important to make sure the SBC sets or clears all address signals as appropriate before the bus cycle is asserted.

| Pin | Name | Function | Pin | Name | Function |

|---|---|---|---|---|---|

| A32 | ISA_ADD_00 | ISA Addr. Bit 0 | B32 | GND | Ground |

| A31 | ISA_ADD_01 | ISA Addr. Bit 1 | B31 | GND | Ground |

| A30 | ISA_ADD_02 | ISA Addr. Bit 2 | B30 | ISA_CLK | 14.3MHz Clock Input |

| A29 | ISA_ADD_03 | ISA Addr. Bit 3 | B29 | +5V | 5 Volt input |

| A28 | ISA_ADD_04 | ISA Addr. Bit 4 | B28 | NC | No Connection |

| A27 | ISA_ADD_05 | ISA Addr. Bit 5 | B27 | NC | No Connection |

| A26 | ISA_ADD_06 | ISA Addr. Bit 6 | B26 | NC | No Connection |

| A25 | ISA_ADD_07 | ISA Addr. Bit 7 | B25 | NC | No Connection |

| A24 | ISA_ADD_08 | ISA Addr. Bit 8 | B24 | GND | Ground |

| A23 | ISA_ADD_09 | ISA Addr. Bit 9 | B23 | NC | No Connection |

| A22 | NC | No Connection | B22 | NC | No Connection |

| A21 | NC | No Connection | B21 | NC | No Connection |

| A20 | NC | No Connection | B20 | NC | No Connection |

| A19 | NC | No Connection | B19 | ISA_ADD_21 | ISA Addr. Bit 21 |

| A18 | NC | No Connection | B18 | NC | No Connection |

| A17 | NC | No Connection | B17 | NC | No Connection |

| A16 | NC | No Connection | B16 | NC | No Connection |

| A15 | NC | No Connection | B15 | NC | No Connection |

| A14 | NC | No Connection | B14 | IOR# | IO Read (Active Low) |

| A13 | ISA_ADD_18 | ISA Addr. Bit 18 | B13 | IOW# | IO Write (Active Low) |

| A12 | ISA_ADD_19 | ISA Addr. Bit 19 | B12 | MEMR# | Mem Read (Active Low) |

| A11 | ISA_ADD_20 | ISA Addr. Bit 20 | B11 | MEMW# | Mem Write (Active Low) |

| A10 | NC | No Connection | B10 | GND | Ground (DANGER!) |

| A9 | ISA_DAT_0 | ISA Data Bit 0 | B9 | NC | No Connect |

| A8 | ISA_DAT_1 | ISA Data Bit 1 | B8 | NC | No Connect |

| A7 | ISA_DAT_2 | ISA Data Bit 2 | B7 | NC | No Connect |

| A6 | ISA_DAT_3 | ISA Data Bit 3 | B6 | NC | No Connect |

| A5 | ISA_DAT_4 | ISA Data Bit 4 | B5 | NC | No Connect |

| A4 | ISA_DAT_5 | ISA Data Bit 5 | B4 | NC | No Connect |

| A3 | ISA_DAT_6 | ISA Data bit 6 | B3 | +5V | 5 Volt Input |

| A2 | ISA_DAT_7 | ISA Data Bit 7 | B2 | ISA_RESET | ISA Reset |

| A1 | NC | No Connection | B1 | GND | Ground |

Usage with 3rd party devices

Please note that while efforts are made to follow the PC/104 specification this peripheral is not tested with third party SBCs or connected peripherals. This card is not guaranteed to operate as intended when third party PC104 peripherals or SBCs are connected.