TS-8820-4100

| |

| Product Page | |

| Image Gallery | |

| Documentation | |

|---|---|

| Schematic | |

| Software Support | |

| TS-8820 source directory | |

| Dimensions (in enclosure) | |

| 6.35 inches (tall) by 7.714 inches (wide including DB9) by 1.14 inches (deep) |

Overview

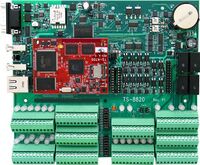

The TS-8820-BOX is a rugged, feature-rich TS-SOCKET based baseboard and System-on-Module (SoM) combination for industrial applications. The TS-8820-BOX is powered by the TS-4100, TS-4700, TS-4710, TS-4720 or TS-4800 System-on-Module devices. The TS-8820-BOX enclosure exposes all of the available I/O on rugged screw terminals while protecting the SoM and other sensitive electronics. The TS-8820-BOX a tough, durable, flexible, powerful, and affordable industrial process control platform.

TS-4100

See the TS-4100 page for functionality regarding the CPU, FPGA, and OS.

|

NXP i.MX6ul 528MHz Cortex-A7 (ARMv7) |

Getting Started

- Place the TS-8820 base board on a firm non-conductive surface.

- Carefully, insert the Computer-on-Module device by aligning and pressing evenly and firmly onto the pair of mating connectors

- Connect the console serial terminal cable

- Connect the Ethernet cable if applicable.

- Connect the GND and POWER screw terminals to a voltage source from 10 V to 30 V DC.

- Alternatively, the unit can be powered via IEEE 802.3af PoE

- Apply power

- Monitor the device bootup using a terminal emulator connected to the serial console port to verify that the board is operating properly

See the TS-4100 page for more details on dealing with the functionality of the CoM.

TS-8820-4100 MUXBUS Interface

The TS-4100 uses the MUXBUS protocol to read and write the TS-8820 FPGA registers. The TS-4100 FPGA does not natively support the MUXBUS protocol in any way, however all of the relevant connection pins are accessible to the TS-4100 FPGA as GPIO pins. In order to facilitate the communication, the TS-4100 ZPU is loaded with a program that is designed to accept data from the CPU and perform MUXBUS bus cycles by directly manipulating the FPGA GPIO pins.

Loading the MUXBUS Application

The utility 'tszpuctl' is used to compile applications, load them in to the ZPU, perform ZPU reset, dump ZPU RAM, and get basic information about the ZPU itself. The sources for 'tszpuctl' as well as the "zpu_muxbus" application are available from the ts4100-utils github repository.

The ZPU can be loaded with the MUXBUS application with the following commands:

git clone https://github.com/embeddedarm/ts4100-utils

tszpuctl -l ts4100-utils/src/zpu/zpu_muxbus.c

Note that the ZPU must be re-loaded with this application each time the unit is booted up. The program is loaded directly in to ZPU RAM and executed from there. It is also possible to compile the "zpu_muxbus.c" file to a .bin file and pass that to 'tszpuctl' for faster loading.

Using the ts8820ctl Application

With the ZPU loaded, it is now ready to accept commands to read and write TS-8820 FPGA registers. Many of the TS-880 features listed below show an example of using "ts8820ctl" to interact with I/O or other peripherals. The 'ts8820ctl' application is included in the stock TS-4100 image and requires the ZPU be loaded with the "zpu_muxbus" application first. If the ZPU is not loaded, 'ts8820ctl' will return with an error indicating that it was unable to communicate with the ZPU.

Custom Applications

The 'ts8820ctl' application is meant as a demo application. While it can be used on its own it may be necessary to integrate its features in to a larger application. It is this reason that 'ts8820ctl' is broken down in to multiple layers.

The top level "src/ts8820ctl.c" file in the ts4100-utils github repository is the commandline interface. From there it makes a number of calls to functions provided by "src/ts8820.c". These functions do the heavy lifting of formatting data and making calls to the ZPU via a custom FIFO interface. The functions in "ts8820.c" can be called from other applications to directly manipulate the TS-8820 peripherals.

Features

FPGA

The TS-8820 is powered by a Lattice XP2 FPGA with 5000 LUTs. Many of the features of the TS-8820 are driven by logic in this FPGA. The CoM attached to the TS-8820 will likely also have an FPGA, but all mentions of an FPGA in this document reference the FPGA on the TS-8820 itself.

The CoM communicates with the TS-8820 FPGA using the MUXBUS, a simple address/data bus defined by Technologic Systems. Application developers do not need to understand the hardware layers involved to read/write the TS-8820 register map. See the demo application source, ts8820ctl.c, for more information on the software interface for the TS-8820.

For applications that require custom logic or interfaces please contact us regarding FPGA customization.

Battery Socket

The coin cell battery is not required for normal TS-8820 operation. The battery provides backup power for the battery backed SRAM and for the real time clock located on the SoM. Without a battery, however, a loss of power will result in a loss of RTC time in the SoM and SRAM data on the TS-8820.

Digital Outputs

The TS-8820 offers 6 digital outputs. OUT1 through OUT4 are isolated and act as a solid state relay capable of switching up to 40 VDC at 1 A continuous draw. OUT5 and OUT6 are non-isolated, able to sink up to 1 A continuous current, and are 40 VDC tolerant.

The outputs can be controlled directly through the 'ts8820ctl' application. See "ts8820ctl.c" and "ts8820.c" for examples of how this writes to the TS-8820 registers.

With the 'ts8820ctl' application, all 6 outputs are manipulated in a single command. That is, a 6-bit value is passed as an argument, and that value is directly set to the outputs. For example, to set OUT5:

ts8820ctl --setdio=0x10

When an output is activated its associated LED indicator is enabled to provide visual feedback.

Isolated Outputs

Digital outputs OUT1 through OUT4 are isolated, each having their own positive and negative terminal. Each isolated output acts as a solid state relay allowing current to flow through the contacts only when it is activated. The isolated outputs are able to switch up to 40 VDC at 1 A continuous current draw. Isolated output terminals are made available on the P7 terminal block.

Non-Isolated Outputs

Digital outputs OUT5 and OUT6 are non-isolated, they rely on the main TS-8820 ground and only have a single contact. Each non-isolated output is a low side switch capable of sinking current when activated. The non-isolated outputs are capable of sinking 1 A continuous current with 40 V input voltage. Non-isolated input terminals appear on the P2 terminal block.

PWM

The TS-8820 has 6 PWM outputs. PWM channels 1 to 6 feed digital outputs 1 to 6 respectively when the PWM override bit is set for a given output.

For all 8 PWM channels, the PWM frequency is approximately (12207/(2^prescaler)) Hz, where the prescaler value is 3 bits wide. That is, a prescaler value of 0 through 7. The PWM duty cycle has 12 bits of resolution. If bit 12 of a PWM register is set, then the PWM output for that channel will be 100% high. Otherwise, the duty cycle setting is divided by 4096 to give the effective duty cycle.

To give OUT5 a ~3 kHZ 50% duty cycle PWM output using ts8820ctl, the following arguments would be used:

# -P sets the PWM frequency via a prescaler value to (12207/(2^VALUE))Hz.

# --mvolts= sets the PWM duty cycle percentage from a decimal scale of 0-10000

# --pwm= PWM channel to enable and modify

ts8820ctl --pwm=5 --mvolts=5000 -P 2

Digital Inputs

The TS-8820 offers 14 digital input pins. There are 8 isolated inputs that are 30 V tolerant. The 6 non-isolated inputs are 40 V tolerant.

The inputs can be polled directly through the ts8820ctl application. See ts8820ctl.c and ts8820.c for examples of how this reads from the TS-8820 registers.

With the ts8820ctl application, all 14 inputs can be read with a single command. A 14-bit value is returned in hex in a format that can be parsed easily by scripting languages. For example, the following output indicates that IN1 and IN3 are active:

ts8820ctl --getdio

dio=0x5

When an input is activated its associated LED indicator is enabled to provide visual feedback.

Isolated Inputs

Digital inputs IN1 though IN8 are isolated, each having their own positive and negative terminal. In order to activate an input, a potential of at least 1.4 VDC and not more than 30 VDC must be generated across these terminals. Isolated input terminals are located on P1 and P7 terminal blocks.

Buffered Inputs

Digital inputs IN9 through IN14 are non-isolated, buffered, active low inputs. Each pin has a nominal threshold of 2.5 VDC, a 3.24 Kohm pull-up to 5 VDC, and are 40 VDC tolerant. Non-isolated inputs are located on the P2 terminal block.

Pulse Counter

Each of the 14 digital inputs has an associated 16-bit pulse counter. The counters are reset at power on, and continue counting through their entire 16 bit range before rolling over. There is no mechanism to clear the counters arbitrarily.

Each counter is incremented once per transition of the associated IN channel, on the asserted edge of the signal. IN1-IN8 counters increase when a positive voltage is applied while IN9-IN14 counters increment when the pin is grounded. The pulse counters do not increment when the signal is returning to its deasserted state.

| Note: | The counter logic does not include any debounce; care should be taken when using the pulse counter for a mechanical contact closure to ensure an accurate count. |

The current count for any given channel can be acquired with:

ts8820ctl --counter <in>

ts8820ctl --counter 10

# Returns the output of

counter10=4

ADC Channels

The TS-8820 offers 16 channels of single ended bi-polar ADC inputs. These ADC inputs are provided by two separate 8 channel ADC devices. Each ADC controller supports a selectable voltage (via GPIO from the SoM, see below) ranges of -5 V to +5 V as well as -10 V to +10 V. This means that each set of 8 channels can be set to different ranges. Each set of 8 channels are sampled simultaneously inside the ADC device.

All 16 ADC inputs are located on the P3, P4, and P5 terminal blocks. While each ADC has a pair of inputs, they are single ended ADC channels; all negative input terminals connect to the TS-8820 common ground.

Additionally, the ADC devices support a number of oversampling options, also controlled via GPIO from the SoM. Enabling oversampling has the effect of adding a digital filter function after the ADC. Increasing the oversampling ratio will decrease the effective sampling rate of the ADC but will increase the signal to noise ratio of each channel. The oversampling rate is shared between both ADC devices, that is, the rate can not be independently set per-device.

Setting the ADC voltage range:

| DIO | Val | Range |

|---|---|---|

| CN2_56 | 1 | -10 V to +10 V |

| CN2_56 | 0 | -5 V to +5 V |

| DIO | Val | Range |

|---|---|---|

| CN2_58 | 1 | -10 V to +10 V |

| CN2_58 | 0 | -5 V to +5 V |

Setting the oversampling rate:

| CN2_64 | CN2_62 | CN2_60 | OS Rate |

|---|---|---|---|

| 0 | 0 | 0 | N/A |

| 0 | 0 | 1 | 2 |

| 0 | 1 | 0 | 4 |

| 0 | 1 | 1 | 8 |

| 1 | 0 | 0 | 16 |

| 1 | 0 | 1 | 32 |

| 1 | 1 | 0 | 64 |

| 1 | 1 | 1 | Invalid |

| Note: | SoM GPIO pins will usually start as inputs with pull up resistors. Therefore the default range will likely be -10 V to +10 V with an invalid oversampling rate. It is advised to set up these pins before acquiring ADC samples. |

Current Loops (4-20 mA measurement)

All 16 ADC channels independently support 4-20 mA current loop measurements. This is achieved by setting a pin jumper for the respective channel on the current loop enable pin header. Setting a jumper will electrically enable a 220 Ω 0.5% resistor from the ADC channel to ground allowing for a constant current measurement.

Thermistor

The TS-8820 supports up to 8 thermistors on channels 1 though 8. Support for a thermistor is enabled via software, the ADC pullup bit of TS-8820 FPGA register 0x2. Setting bit 8 enables a pull up on ADC channels 1 and 2, setting bit 9 enables a pull up on ADC channels 3 and 4, and setting bit 10 enables a pull up on channels 5 through 8. When enabled, each channel will get a separate 6.04 kΩ resistor to +12.5 V allowing the use of a thermistor probe.

ADC Usage

The 'ts8820ctl' application can be used to quickly sample the ADCs. This will send simultaneous sampling commands to each of the two ADC devices which will then sample all 16 channels in total the amount of times specified. See the "ts8820ctl.c" and "ts8820.c" files for examples on how this operation takes place.

For example, to sample all of the channels 5 times, the following command would be used:

ts8820ctl --sample=5

Collected 80 samples total.

Ch 1 Ch 2 Ch 3 Ch 4 Ch 5 Ch 6 Ch 7 Ch 8 Ch 9 Ch10 Ch11 Ch12 Ch13 Ch14 Ch15 Ch16

---- ---- ---- ---- ---- ---- ---- ---- ---- ---- ---- ---- ---- ---- ---- ----

-7626 2195 2193 2199 2192 2195 2195 2192 2189 2189 2193 2190 2189 2192 2191 2191

-7626 2194 2192 2198 2191 2194 2194 2191 2188 2189 2192 2189 2188 2191 2189 2190

-7626 2193 2191 2197 2190 2193 2193 2190 2187 2188 2191 2188 2186 2190 2189 2189

-7626 2189 2188 2193 2186 2189 2190 2186 2183 2184 2187 2184 2183 2186 2185 2185

-7626 2189 2187 2192 2186 2188 2189 2186 2183 2183 2187 2184 2182 2185 2184 2185

Above, channel 1 has a -7.62 V voltage source attached to it, all other channels are left unconnected. The range is set at -10 V to +10 V, and the oversampling rate is set to 64.

Note that on the TS-4100, the range defaults to -5 V to +5 V and oversampling is in the "invalid" state due to how the GPIO pins are set up in the CPU.

Before the above measurement was taken, the following commands were run on the TS-4100 in order to set the correct range and oversampling rate:

echo 120 > /sys/class/gpio/export

echo 121 > /sys/class/gpio/export

echo 122 > /sys/class/gpio/export

echo low > /sys/class/gpio/gpio120/direction

echo high > /sys/class/gpio/gpio121/direction

echo high > /sys/class/gpio/gpio122/direction

echo 119 > /sys/class/gpio/export

echo 118 > /sys/class/gpio/export

echo high > /sys/class/gpio/gpio118/direction

echo high > /sys/class/gpio/gpio119/direction

These GPIO states must be set each time the unit is powered up.

DAC Channels

The TS-8820 has 4 channels of 0 to +10 V DAC outputs. Each DAC channel has a positive and negative terminal connection. The negative side of the terminals are connected to the common ground of the TS-8820 and are non-isolated. The DAC terminals are on the P3 and P9 terminal blocks.

The DAC channels each have 12 bits of resolution that correspond to 0 to +10 V output. The upper bit (bit 15) of each register is a control bit that is used to synchronize the output of all 4 DAC channels. This means that all four registers can be updated without modifying the actual DAC output. Setting the control bit of any DAC channel register will case an update of the DAC output of all four channels. If the DAC register has not been modified, the update will still be sent but the actual output will remain the same. Reading this control bit will indicate if the synchronization is complete. Writing the DAC registers while the control bit is still asserted, indicating busy, will result in undefined behavior. The update process from setting the control bit to its completion takes approximately 3 microseconds.

When 0 is written to the control bit, the DAC values are updated internally in the FPGA but not transferred to the DAC. Thus any set of channels can be updated simultaneously by only writing a one on the final write.

The DAC channels can be controlled through 'ts8820ctl'. Note that the "--setdac" option to 'ts8820ctl' will always set the control bit of the selected register. See "ts8820ctl.c" and "ts8820.c" for an example of how this process works.

The following command would set DAC output 1 to 0.5 V:

ts8820ctl --setdac=1 --mvolts=500

Isolated CAN Port

The TS-8820 provides an isolated CAN port on the P10 terminal block. The CAN interface itself is from the SoM with the TS-8820 facilitating the isolated physical interface.

Optionally, a 124 ohm termination resistor can be electrically added by setting the Term. CAN jumper.

More information about the CAN interface is available in the TS-4100 manual.

Isolated RS-232

The TS-8820 provides a single isolated RS-232 port on the P10 terminal block. The UART interface itself is from the SoM with the TS-8820 facilitating the isolated RS-232 physical interface.

By default, this UART port is connected to the ttymxc1 device on the TS-4100.

Isolated RS-485

The TS-8820 provides a single isolated RS-485 port on the P10 terminal block. The UART interface itself is from the SoM with the TS-8820 facilitating the isolated RS-485 physical interface.

Optionally, a 124 ohm termination resistor can be electrically added by setting the Term. 485 jumper.

By default, this port is connected to the ttymxc3 on the TS-4100. The TS-4100 uses an automatic TXEN for half-duplex RS-485 handled by a CPU GPIO pin. However in order for this to function, it is necessary to modify the TS-4100 FPGA crossbar mux to route this CPU GPIO pin to the TXEN pin on the TS-8820. The following command needs to be run each time the unit is powered on in order for RS-485 to properly function:

tshwctl --addr 177 --poke 2

This connects the CPU GPIO pin directly to the RS-485 TXEN pin on the TS-8820 via internal switches in the TS-4100 FPGA.

Relays

The TS-8820 provides 4 mechanical SPDT relays. Each relay has a common connection, a normally open (NO), and normally closed (NC) contact. All 4 sets of contacts are located on the P8 terminal block.

Each relay has contacts rated for 277 VAC / 30 VDC @ 5 A (NO contacts) and 3 A (NC contacts). The use of these relays in the TS-8820 are rated for 30 VAC / 30 VDC @ 5 A (NO) and 3 A (NC).

These 4 relays are manipulated by GPIO from the SoM, not the TS-8820 itself. The relays are controlled by the following GPIO pins:

See the TS-4100 GPIO manual for information on how to manipulate the GPIO for the relays.

Power Supply

The TS-8820 can be powered via PoE or direct DC voltage input to the terminal block connectors. If PoE is not used, power must be supplied on terminal block P6.

DC via Terminal Blocks

Direct power input can be applied to the P6 terminal block. There are three terminals for power and three for a ground connection. Each of the three sets of terminals are electrically connected together internally in the TS-8820. Operational range of the TS-8820 is +10 VDC to +30 VDC on these inputs. Supply an external ground on terminal 10, 11, and/or 12. Supply +10 V to +30 V on terminal 7, 8, and/or 9.

802.3af PoE

The TS-8820 is IEEE 802.3af PoE compliant. This allows the whole unit to be powered directly from a PoE sourcing device.

When powered via PoE, +24 VDC is made available on the P6 terminal block power terminals. Ensure that the total power draw of the system does not exceed the limits defined by IEEE 802.3af and that power is not also supplied to the TS-8820 on these pins!

LEDs

The TS-8820 has 27 LEDs used to indicate the electrical status of the inputs and outputs on the device. LEDs are labelled as "LED#" on the PCB silkscreen.

The majority of the LEDs are not able to be directly controlled, they turn on or off as a reaction to the status of the I/O they are connected to. For example, when DIG_OUT1 is set, LED17 will turn on. The "System" LEDs are the exception to this and are controlled via the SoM LED interface.

| LED | FUNCTION | --- | LED | FUNCTION |

|---|---|---|---|---|

| 1 | System RED_LED | 2 | Doesn't exist. | |

| 3 | System Power | 4 | System GREEN_LED | |

| 5 | RELAY_1 | 6 | RELAY_2 | |

| 7 | RELAY_3 | 8 | RELAY_4 | |

| 9 | DIG_IN1 | 10 | DIG_IN2 | |

| 11 | DIG_IN3 | 12 | DIG_IN4 | |

| 13 | DIG_IN5 | 14 | DIG_IN6 | |

| 15 | DIG_IN7 | 16 | DIG_IN8 | |

| 17 | DIG_OUT1 | 18 | DIG_OUT2 | |

| 19 | DIG_OUT3 | 20 | DIG_OUT4 | |

| 21 | DIG_IN9 | 22 | DIG_IN10 | |

| 23 | DIG_IN11 | 24 | DIG_IN12 | |

| 25 | DIG_IN13 | 26 | DIG_IN14 | |

| 27 | DIG_OUT5 | 28 | DIG_OUT6 |

External Interfaces

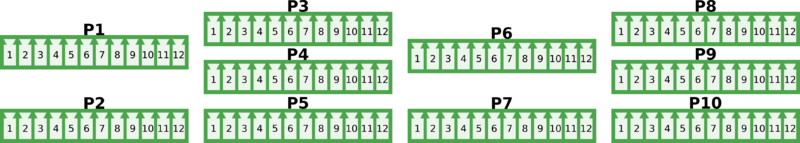

Terminal Blocks

| Note: | If you have a REV A board disregard the P1-P10 labeling as printed on the PCB. |

|

|

|

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

Ethernet Connector

The TS-8820 can connect to any Ethernet LAN. The Ethernet connector includes LEDs indicating link and activity. The link LED should be on whenever the TS-8820 is powered and connected to a LAN. This connector allows the TS-8820 to be powered by PoE.

USB Host

The USB is available on two ports as a USB 2.0 host.

|

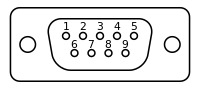

DB9 Connector

|

|

Register Map

Most of the access to the I/O is abstracted by 'ts8820ctl' and "ts8820.c", but it is also possible to access them directly through MUXBUS registers if applicable.

| Offset | Bits | Description |

|---|---|---|

| 0x0 | 15:0 | Model ID: Reads 0x8820 |

| 0x2 | 15:11 | Reserved |

| 10 | Pull-up 5-8 enable | |

| 9 | Pull-up 3-4 enable | |

| 8 | Pull-up 1-2 enable | |

| 7 | H-bridge 2 enable (contacts go high-Z otherwise) | |

| 6 | H-bridge 1 enable (contacts go high-Z otherwise) | |

| 5 | H-bridge 2 direction | |

| 4 | H-bridge 1 direction | |

| 3:0 | FPGA Revision | |

| 0x4 | 15:14 | Reserved |

| 13:0 | Digital inputs 14:1 | |

| 0x6 | 15:10 | Reserved |

| 9:0 | SRAM Page register | |

| 0x8 | 15:12 | Reserved |

| 11:6 | Override Digital Outputs 6:1 with PWM | |

| 5:0 | Digital Output Values 6:1 | |

| 0xa | 15:0 | Reserved |

| 0xc | 15:0 | Reserved |

| 0xe | 15:0 | Reserved |

| 0x10 | 15:13 | PWM #1 Prescaler |

| 12:0 | PWM #1 Duty Cycle | |

| 0x12 | 15:13 | PWM #2 Prescalar |

| 12:0 | PWM #2 Duty Cycle | |

| 0x14 | 15:13 | PWM #3 Prescaler |

| 12:0 | PWM #3 Duty Cycle | |

| 0x16 | 15:13 | PWM #4 Prescaler |

| 12:0 | PWM #4 Duty Cycle | |

| 0x18 | 15:13 | PWM #5 Prescaler |

| 12:0 | PWM #5 Duty Cycle | |

| 0x1a | 15:13 | PWM #6 Prescaler |

| 12:0 | PWM #6 Duty Cycle | |

| 0x1c | 15:13 | PWM #7 Prescaler (H Bridge 1) |

| 12:0 | PWM #7 Duty Cycle (H Bridge 1) | |

| 0x1e | 15:13 | PWM #8 Prescaler (H Bridge 2) |

| 12:0 | PWM #8 Duty Cycle (H Bridge 2) | |

| 0x20 | 15:0 | Pulse Counter #1 (RO) |

| 0x22 | 15:0 | Pulse Counter #2 (RO) |

| 0x24 | 15:0 | Pulse Counter #3 (RO) |

| 0x26 | 15:0 | Pulse Counter #4 (RO) |

| 0x28 | 15:0 | Pulse Counter #5 (RO) |

| 0x2a | 15:0 | Pulse Counter #6 (RO) |

| 0x2c | 15:0 | Pulse Counter #7 (RO) |

| 0x2e | 15:0 | Pulse Counter #8 (RO) |

| 0x30 | 15:0 | Pulse Counter #9 (RO) |

| 0x32 | 15:0 | Pulse Counter #10 (RO) |

| 0x34 | 15:0 | Pulse Counter #11 (RO) |

| 0x36 | 15:0 | Pulse Counter #12 (RO) |

| 0x38 | 15:0 | Pulse Counter #13 (RO) |

| 0x3a | 15:0 | Pulse Counter #14 (RO) |

| 0x3c | 15:0 | Reserved |

| 0x3e | 15:0 | Reserved |

| 0x80 | 15:0 | ADC Core ID (reads 0xadc1) |

| 0x82 | 15:8 | ADC Channel Mask (0 = do not save channel data) |

| 7:6 | Highest number chip to use (0-3, if 01 then sample chip 0 and chip 1) | |

| 5 | 1 = Force standby | |

| 4 | 1 = Use standby between samples to save power | |

| 3 | 1 = Smart DMA IRQ mode | |

| 2 | 1 = Enable IRQ | |

| 1 | 1 = Collect samples, 0 = stop | |

| 0 | 1 = Reset ADC chips and all FIFOs | |

| 0x84 | 15 | 1 = There has been a FIFO overflow since last reset |

| 14:0 | Number of samples available to be read | |

| 0x86 | 15:0 | Sample Data (RO) |

| 0x88 | 15:0 | Sampling period LSB (RW) |

| 0x8a | 15:0 | Sampling period MSB (RW) |

| 0x8c | 15:0 | IRQ Threshold (RW) |

| 0x8e | 15:0 | Reserved |

| 0x90 | 15:0 | Reserved |

| 0x92 | 15:0 | Reserved |

| 0x94 | 15:0 | Reserved |

| 0x96 | 15:0 | Reserved |

| 0x98 | 15:0 | Reserved |

| 0x9a | 15:0 | Reserved |

| 0x9c | 15:0 | Reserved |

| 0x9e | 15:0 | Reserved |

| 0xa0 | 15:0 | DAC 1 Control Register |

| 0xa2 | 15:0 | DAC 2 Control Register |

| 0xa4 | 15:0 | DAC 3 Control Register |

| 0xa6 | 15:0 | DAC 4 Control Register |

Product Notes

FCC Advisory

This equipment generates, uses, and can radiate radio frequency energy and if not installed and used properly (that is, in strict accordance with the manufacturer's instructions), may cause interference to radio and television reception. It has been type tested and found to comply with the limits for a Class A digital device in accordance with the specifications in Part 15 of FCC Rules, which are designed to provide reasonable protection against such interference when operated in a commercial environment. Operation of this equipment in a residential area is likely to cause interference, in which case the owner will be required to correct the interference at his own expense.

If this equipment does cause interference, which can be determined by turning the unit on and off, the user is encouraged to try the following measures to correct the interference:

Reorient the receiving antenna. Relocate the unit with respect to the receiver. Plug the unit into a different outlet so that the unit and receiver are on different branch circuits. Ensure that mounting screws and connector attachment screws are tightly secured. Ensure that good quality, shielded, and grounded cables are used for all data communications. If necessary, the user should consult the dealer or an experienced radio/television technician for additional suggestions. The following booklets prepared by the Federal Communications Commission (FCC) may also prove helpful:

How to Identify and Resolve Radio-TV Interference Problems (Stock No. 004-000-000345-4) Interface Handbook (Stock No. 004-000-004505-7) These booklets may be purchased from the Superintendent of Documents, U.S. Government Printing Office, Washington, DC 20402.

Limited Warranty

See our Terms and Conditions for more details.