TS-8820-4700

| |

| Product Page | |

| Image Gallery |

Overview

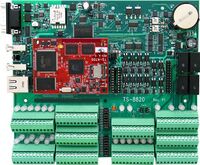

The TS-8820-BOX is a rugged, feature-rich TS-SOCKET based baseboard and Macrocontroller combination for industrial applications. Powered by either the TS-4700 or TS-4800 Macrocontroller Computer on Module, the TS-8820-BOX provides a variety of electrically isolated I/O.. The TS-8820-BOX enclosure exposes the I/O on rugged screw terminals while protecting the macrocontroller and other sensitive electronics. The TS-8820-BOX with an 800MHz TS-4700 or TS-4800 in the aluminum enclosure provides a tough, durable, flexible, powerful, and affordable industrial process control system platform.

TS-4700

See the TS-4700 page for functionality regarding the CPU, FPGA, and OS.

|

Marvell PXA166 800MHz ARM9 |

Getting Started

- Place the TS-8820 base board on a firm non-conductive surface.

- Carefully, insert the TS-4000 Series Macrocontroller by aligning and pressing evenly and firmly onto the pair of mating connectors

- Connect the console serial terminal cable

- Connect the Ethernet cable if applicable.

- Connect the GND and POWER screw terminals to a voltage source from 10V to 30V DC.

- Alternatively, the board can be powered through POE

- Apply power

- Monitor the TS-SOCKET SBC using a terminal emulator connected to the serial console port to verify that the board is operating properly

See the TS-4700 page for more details on dealing with the functionality of the macrocontroller.

Features

PWM

PWMs 1 to 6 feed digital outputs 1 to 6, respectively, only if the PWM override bit is set for the output in question. PWMs 7 and 8 are used for H-bridges. If an H-bridge is not enabled, both contacts will be high impedance. If it is enabled, it will have one side tied to ground and the other side driven by the PWM. The direction bit can be toggled at any time to toggle the H-bridge direction. "Brake mode" with both sides high is not supported by the current FPGA version.

For all 8 PWMs, the PWM frequency is approximately 12207/(2^prescalar). PWM duty cycle has 12 bits of resolution. If bit 13 is set, the output will be 100% high. Otherwise, the duty cycle setting is divided by 4096 to give the effective duty cycle.

DAC

DAC output registers have 12 data bits (bits 11:0) and one control bit (bit 15). Bits 14:12 are reserved. The control bit is used for synchronization of output voltage updates across multiple channels if necessary and for ensuring software compliance with hardware requirements. When a 1 is written to the control bit, DAC data is sent to all channels even if it has not been changed since the last update. After an update is initiated, software can read the control bit to see if the system is still busy. Further writes of DAC values while the hardware is busy will result in undefined behavior. The update process takes approximately 3 microseconds.

When 0 is written to the control bit, the DAC values are updated internally in the FPGA but not transferred to the DAC. Thus any set of channels can be updated simultaneously by only writing a one on the final write.

LEDS

The TS-8820 has 27 LED indicators. Most are used to provide instant visual confirmation of the states of DIO and relays. Each LED is labeled on the silkscreen.

LED5 to LED8 indicate relay 1 to relay 4 are activated, respectively.

LED9 to LED16 correspond with digital inputs 1 to 8.

LED17 to LED20 correspond with digital outputs 1 to 4.

LED21 to LED26 correspond with digital inputs 9 to 14.

LED27 and LED28 correspond with digital outputs 5 and 6.

LED3 indicates power is supplied to the TS-8820. LED1 and LED4 are connected to the standard red and green LED lines used on most TS-SOCKET systems.

Connectors

Terminal Blocks

| Pin | Description |

|---|---|

| 1 | IN1+ |

| 2 | IN1- |

| 3 | IN2+ |

| 4 | IN2- |

| 5 | IN3+ |

| 6 | IN3- |

| 7 | IN4+ |

| 8 | IN4- |

| 9 | IN5+ |

| 10 | IN5- |

| 11 | IN6+ |

| 12 | IN6- |

| Pin | Description |

|---|---|

| 1 | HB_OUT1 |

| 2 | HB_OUT2 |

| 3 | HB_OUT3 |

| 4 | HB_OUT4 |

| 5 | Ground |

| 6 | Ground |

| 7 | EXT_12V_24V |

| 8 | EXT_12V_24V |

| 9 | EXT_12V_24V |

| 10 | EXT_POWER_RET |

| 11 | EXT_POWER_RET |

| 12 | EXT_POWER_RET |

| Pin | Description |

|---|---|

| 1 | IN7+ |

| 2 | IN7- |

| 3 | IN8+ |

| 4 | IN8- |

| 5 | OUT1+ |

| 6 | OUT1- |

| 7 | OUT2+ |

| 8 | OUT2- |

| 9 | OUT3+ |

| 10 | OUT3- |

| 11 | OUT4+ |

| 12 | OUT4- |

| Pin | Description |

|---|---|

| 1 | ADC Channel 1 |

| 2 | Ground |

| 3 | ADC Channel 2 |

| 4 | Ground |

| 5 | ADC Channel 3 |

| 6 | Ground |

| 7 | ADC Channel 4 |

| 8 | Ground |

| 9 | ADC Channel 5 |

| 10 | Ground |

| 11 | ADC Channel 6 |

| 12 | Ground |

| Pin | Description |

|---|---|

| 1 | ADC Channel 13 |

| 2 | Ground |

| 3 | ADC Channel 14 |

| 4 | Ground |

| 5 | ADC Channel 15 |

| 6 | Ground |

| 7 | ADC Channel 16 |

| 8 | Ground |

| 9 | DAC 1 |

| 10 | Ground |

| 11 | DAC 2 |

| 12 | Ground |

| Pin | Description |

|---|---|

| 1 | ADC Channel 7 |

| 2 | Ground |

| 3 | ADC Channel 8 |

| 4 | Ground |

| 5 | ADC Channel 9 |

| 6 | Ground |

| 7 | ADC Channel 10 |

| 8 | Ground |

| 9 | ADC Channel 11 |

| 10 | Ground |

| 11 | ADC Channel 12 |

| 12 | Ground |

| Pin | Description |

|---|---|

| 1 | Relay 1 NO |

| 2 | Relay 1 COM |

| 3 | Relay 1 NC |

| 4 | Relay 2 NO |

| 5 | Relay 2 COM |

| 6 | Relay 2 NC |

| 7 | Relay 3 NO |

| 8 | Relay 3 COM |

| 9 | Relay 3 NC |

| 10 | Relay 3 NO |

| 11 | Relay 3 COM |

| 12 | Relay 3 NC |

| Pin | Description |

|---|---|

| 1 | Not Connected |

| 2 | Not Connected |

| 3 | ISO Common |

| 4 | ISO Common |

| 5 | XUART0 ISO RS485+ |

| 6 | XUART0 ISO RS485- |

| 7 | XUART1 ISO RS232 TXD |

| 8 | XUART1 ISO RS232 RXD |

| 9 | Not Connected |

| 10 | CAN Common |

| 11 | CAN_H |

| 12 | CAN_L |

| Pin | Description |

|---|---|

| 1 | IN 9 |

| 2 | IN 10 |

| 3 | Ground |

| 4 | IN 11 |

| 5 | IN 12 |

| 6 | Ground |

| 7 | IN 13 |

| 8 | IN 14 |

| 9 | Ground |

| 10 | OUT 5 |

| 11 | OUT 6 |

| 12 | Ground |

| Pin | Description |

|---|---|

| 1 | DAC 3 |

| 2 | Ground |

| 3 | DAC 4 |

| 4 | Ground |

| 5 | Spare 1 |

| 6 | Spare 2 |

| 7 | Spare 3 |

| 8 | Spare 4 |

| 9 | Spare 5 |

| 10 | Spare 6 |

| 11 | Spare 7 |

| 12 | Spare 8 |

USB Host

The USB is available on two ports as a USB 2.0 host.

|

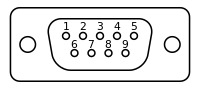

DB9 Connector

|

class=wikitable |

| Pin | Description |

|---|---|

| 1 | XUART4 RS485+ |

| 2 | Debug Console RS232 RXD |

| 3 | Debug Console RS232 TXD |

| 4 | Not Connected |

| 5 | Ground |

| 6 | XUART4 RS485- |

| 7 | XUART2 RS232 TXD |

| 8 | XUART2 RS232 RXD |

| 9 | Not Connected |

Register Map

Most of the access to the IO should be abstracted by ts8820ctl and ts8820.c, but you can also access these IO directly through the MUXBUS registers.

| Offset | Bits | Description |

|---|---|---|

| 0x0 | 15:0 | Model ID: Reads 0x8820 |

| 0x2 | 15:8 | Reserved |

| 7 | H-bridge 2 enable (contacts go high-Z otherwise) | |

| 6 | H-bridge 1 enable (contacts go high-Z otherwise) | |

| 5 | H-bridge 2 direction | |

| 4 | H-bridge 1 direction | |

| 3:0 | FPGA Revision | |

| 0x4 | 15:14 | Reserved |

| 13:0 | Digital inputs 14:1 | |

| 0x6 | 15:10 | Reserved |

| 9:0 | SRAM Page register | |

| 0x8 | 15:12 | Reserved |

| 11:6 | Override Digital Outputs 6:1 with PWM | |

| 5:0 | Digital Output Values 6:1 | |

| 0xa | 15:0 | Reserved |

| 0xc | 15:0 | Reserved |

| 0xe | 15:0 | Reserved |

| 0x10 | 15:13 | PWM #1 Prescaler |

| 12:0 | PWM #1 Duty Cycle | |

| 0x12 | 15:13 | PWM #2 Prescalar |

| 12:0 | PWM #2 Duty Cycle | |

| 0x14 | 15:13 | PWM #3 Prescaler |

| 12:0 | PWM #3 Duty Cycle | |

| 0x16 | 15:13 | PWM #4 Prescaler |

| 12:0 | PWM #4 Duty Cycle | |

| 0x18 | 15:13 | PWM #5 Prescaler |

| 12:0 | PWM #5 Duty Cycle | |

| 0x1a | 15:13 | PWM #6 Prescaler |

| 12:0 | PWM #6 Duty Cycle | |

| 0x1c | 15:13 | PWM #7 Prescaler |

| 12:0 | PWM #7 Duty Cycle | |

| 0x1e | 15:13 | PWM #8 Prescaler |

| 12:0 | PWM #8 Duty Cycle | |

| 0x20 | 15:0 | Pulse Counter #1 |

| 0x22 | 15:0 | Pulse Counter #2 |

| 0x24 | 15:0 | Pulse Counter #3 |

| 0x26 | 15:0 | Pulse Counter #4 |

| 0x28 | 15:0 | Pulse Counter #5 |

| 0x2a | 15:0 | Pulse Counter #6 |

| 0x2c | 15:0 | Pulse Counter #7 |

| 0x2e | 15:0 | Pulse Counter #8 |

| 0x30 | 15:0 | Pulse Counter #9 |

| 0x32 | 15:0 | Pulse Counter #10 |

| 0x34 | 15:0 | Pulse Counter #11 |

| 0x36 | 15:0 | Pulse Counter #12 |

| 0x38 | 15:0 | Pulse Counter #13 |

| 0x3a | 15:0 | Pulse Counter #14 |

| 0x3c | 15:0 | Reserved |

| 0x3e | 15:0 | Reserved |

| 0x80 | 15:0 | ADC Core ID (reads 0xadc1) |

| 0x82 | 15:8 | ADC Channel Mask (0 = do not save channel data) |

| 7:6 | Highest number chip to use (0-3) | |

| 5 | 1 = Force standby | |

| 4 | 1 = Use standby between samples to save power | |

| 3 | 1 = Smart DMA IRQ mode | |

| 2 | 1 = Enable IRQ | |

| 1 | 1 = Collect samples, 0 = stop | |

| 0 | 1 = Reset ADC chips and all FIFOs | |

| 0x84 | 15 | 1 = There has been a FIFO overflow since last reset |

| 14:0 | Number of samples available to be read | |

| 0x86 | 15:0 | Sample Data (RO) |

| 0x88 | 15:0 | Sampling period LSB (RW) |

| 0x8a | 15:0 | Sampling period MSB (RW) |

| 0x8c | 15:0 | IRQ Threshold (RW) |

| 0x8e | 15:0 | DMA transfer size for smart mode (RW) (TODO) |

| 0x90 | 15:0 | Reserved |

| 0x92 | 15:0 | Reserved |

| 0x94 | 15:0 | Reserved |

| 0x96 | 15:0 | Reserved |

| 0x98 | 15:0 | Reserved |

| 0x9a | 15:0 | Reserved |

| 0x9c | 15:0 | Reserved |

| 0x9e | 15:0 | Reserved |

| 0xa0 | 15:0 | DAC 1 Control Register |

| 0xa2 | 15:0 | DAC 2 Control Register |

| 0xa4 | 15:0 | DAC 3 Control Register |

| 0xa6 | 15:0 | DAC 4 Control Register |